Chapter 12 instruction cache, General description, Main body structure – FUJITSU MB91460 SERIES FR60 User Manual

Page 195

179

Chapter 12 Instruction Cache

1.General description

Chapter 12 Instruction Cache

This chapter describes the instruction cache memory included in MB91460 family members and

its operation.

1. General description

The instruction cache is a fast local memory for temporary storage. Once an instruction is

accessed to be fetched from external slower memory, the instruction cache holds the instruction

code inside to increase the speed of accessing the same code from then on. The instruction

cache data RAM and tag RAM are made directly read/write-accessible by software by setting the

RAM mode. To turn off the instruction cache after turning it on once, be sure to use the

subroutine shown in Section 4.2.4 "Settings for handling the I-Cache".

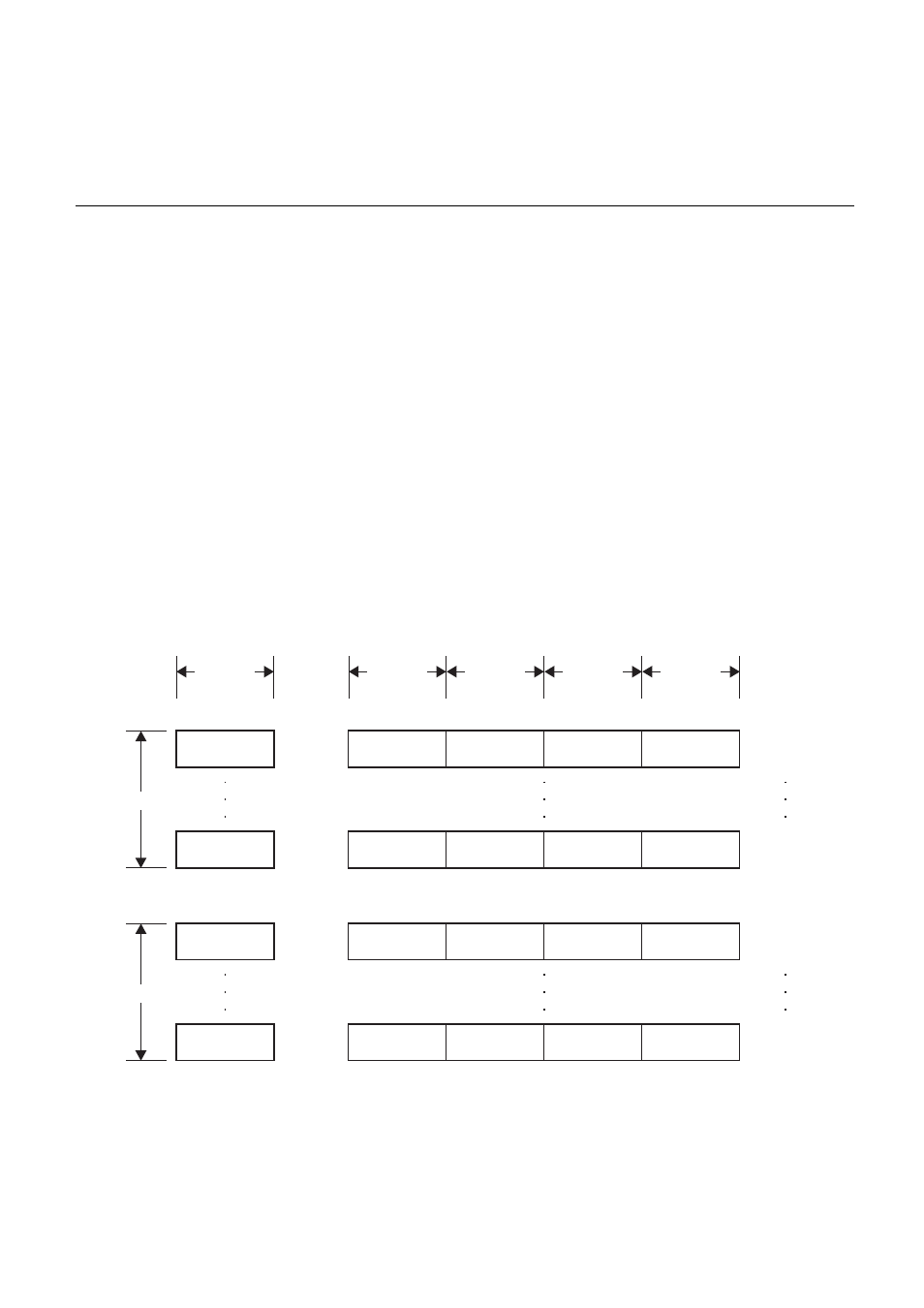

2. Main body structure

•

FR basic instruction length:

2 bytes

•

Block arrangement system:

2-way set associative system

•

Block

128 blocks per way

16 bytes per block (= 4 sub-blocks)

4 bytes per sub-block (= 1 bus access unit)

Figure 2-1 Instruction Cache Structure

Cache tag

Sub-block 0

Block 0

Block 127

Sub-block 1

Sub-block 2

Sub-block 3

Cache tag

Sub-block 0

Sub-block 1

Sub-block 2

Sub-block 3

4 bytes

128 Blocks

4 bytes

I3

4 bytes

I2

4 bytes

I1

4 bytes

I0

Way 1

Cache tag

Sub-block 0

Block 0

Block 127

Sub-block 1

Sub-block 2

Sub-block 3

Cache tag

Sub-block 0

Sub-block 1

Sub-block 2

Sub-block 3

128 Blocks

Way 2