Setting, Q & a, 1 what are interrupt-associated registers – FUJITSU MB91460 SERIES FR60 User Manual

Page 401: 2 how is the interrupt request generated/cleared, Caution, Q & a 7.1 what are interrupt-associated registers

385

Chapter 27 Delayed Interrupt

6.Setting

6. Setting

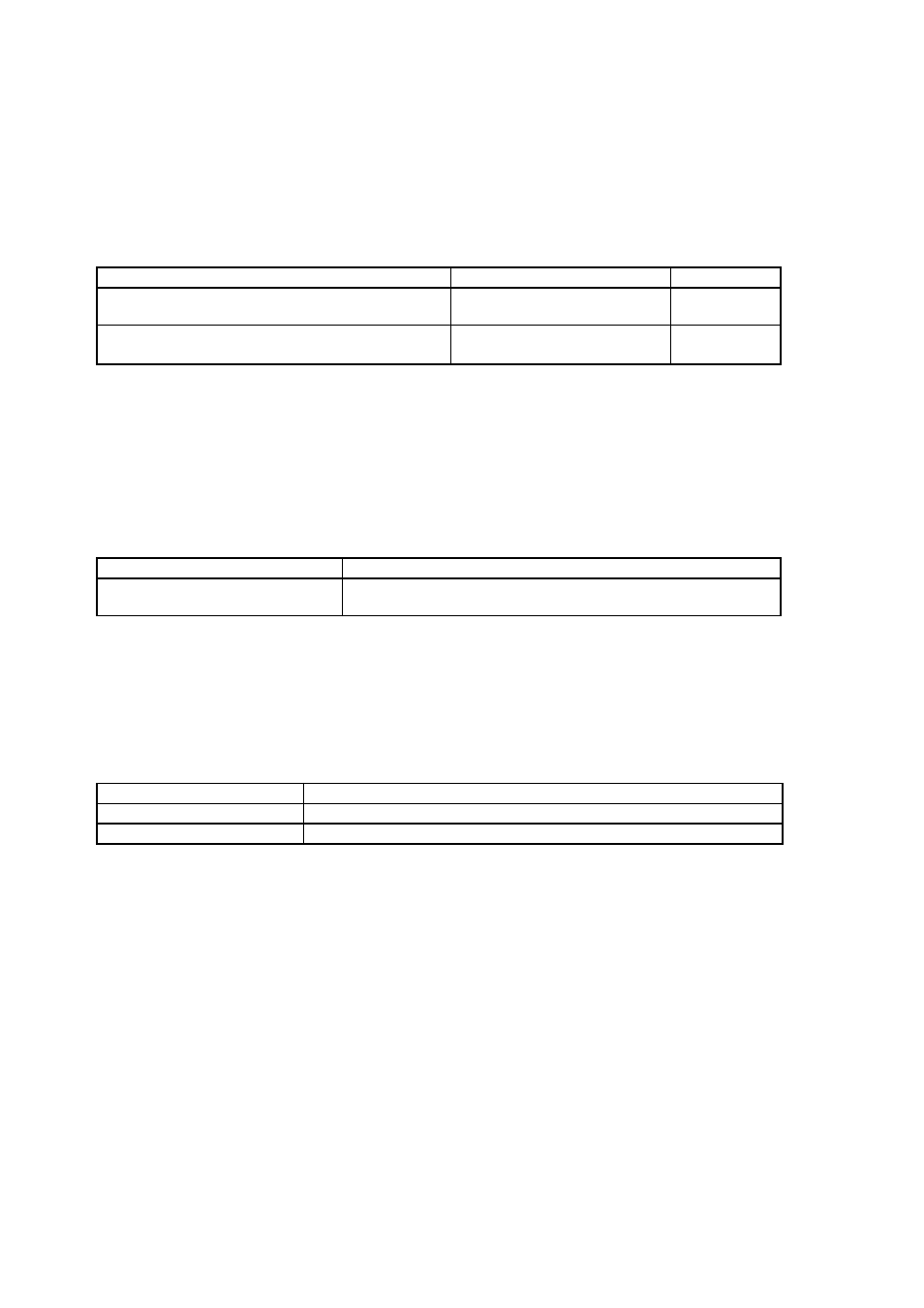

Table Setting required for the delayed interrupt generation/clear

*: Refer to the number for the setting method.

7. Q & A

7.1 What are interrupt-associated registers?

Setting for the delay interrupt vector and interrupt level

The relationship between the delay interrupt level and the delay interrupt vector is shown in the following table.

Refer to “

Chapter 24 Interrupt Control (Page No.311)

” for more information on the interrupt level and interrupt

vector.

The interrupt request bit (DICR.DLYI) cannot automatically be released, and it should be released by the

software before returning from an interrupt service. (“0” is written for DLYI bit)

Remark: For REALOS compatibility reasons, ICR23 and ICR47 can be exchanged by setting the REALOS

compatibility bit (addr 0x0C03 : IOS[0]) if necessary.

7.2 How is the interrupt request generated/cleared?

The delayed interrupt request bit (DICR.DLYI) performs this function.

The delayed interrupt does not have an interrupt request enable bit.

8. Caution

• The delay interrupt request bit is the same as general interrupt request flags. It should be used to clear

delayed interrupt request bit in an interrupt routine in addition to switching tasks.

• The delayed interrupt function can use real time OS (REALOS). As a result, the delayed interrupt function is

prohibited in a piece of user software when using real time OS.

Table 6-1 Setting required for the delay interrupt generation/clear

Setting

Setting register

Setting method*

Vector for delay interrupt

Refer to “

Refer to 7.1

Delayed interrupt setting.

Generating interrupt request/Releasing interrupt request

Delayed interrupt control register

(DICR)

Refer to 7.2

Interrupt vector (default)

Interrupt level setting bit (ICR[4:0])

#63

Address: 0FFF00h

Interrupt level register (ICR23)

Address: 00457h

Interrupt request enable bit (DLYI)

Clearing an interrupt request

Sets the value to “0”

Generating an interrupt request

Sets the value to “1”