3 can protocol related registers – FUJITSU MB91460 SERIES FR60 User Manual

Page 712

696

Chapter 34 CAN Controller

2.Register Description

Additionally the busoff state is reset and the output CAN_TX is set to recessive(HIGH). The value 0x0001 (Init

= ‘1’) in the CAN Control Register enables the software initialisation. The CAN does not influence the CAN bus

until the CPU resets Init to ‘0’.

The data stored in the Message RAM is not affected by a hardware reset. After power-on, the contents of the

Message RAM is undefined.

2.3 CAN Protocol Related Registers

These registers are related to the CAN protocol controller in the CAN Core. They control the operating modes

and the configuration of the CAN bit timing and provide status information.

■

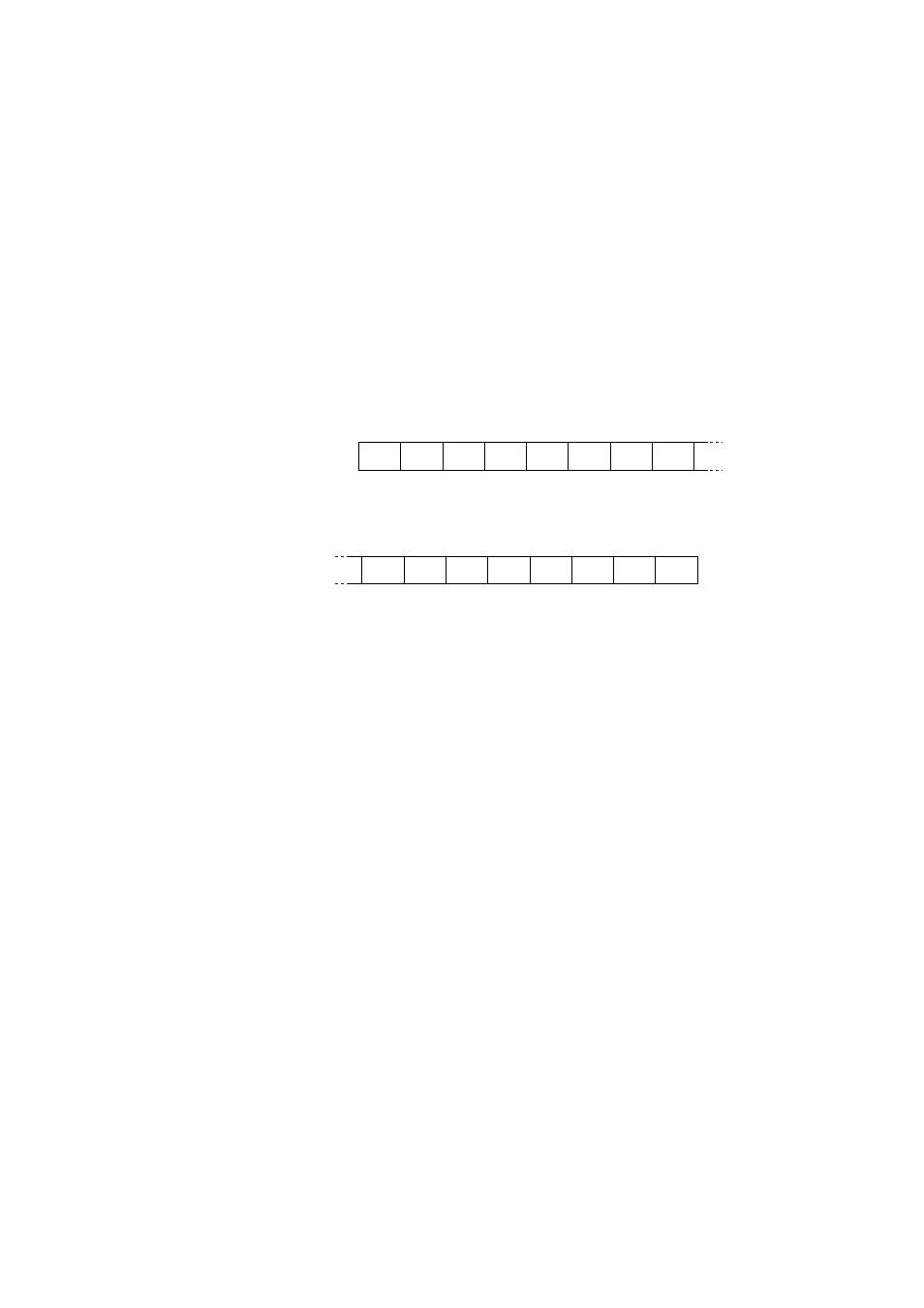

CAN Control Register (CTRLR)

res

res

res

res

res

res

res

res

⇐ Bit no.

Read/write

⇒

(R)

(R)

(R)

(R)

(R)

(R)

(R)

(R)

Default value

⇒

(0)

(0)

(0)

(0)

(0)

(0)

(0)

(0)

CAN Control Register high byte

Address : Base + 0x00

H

15

14

13

12

11

10

9

8

CTRLRH

Test

CCE DAR

res

EIE

SIE

IE

Init

⇐ Bit no.

Read/write

⇒ (R/W) (R/W) (R/W) (R) (R/W) (R/W) (R/W) (R/W)

Default value

⇒

(0)

(0)

(0)

(0)

(0)

(0)

(0)

(1)

Address : Base + 0x01

H

7

6

5

4

3

2

1

0

CTRLRL

CAN Control Register low byte