2 div0r: clock division setting register 0 – FUJITSU MB91460 SERIES FR60 User Manual

Page 209

193

Chapter 13 Clock Control

4.Registers

4.2 DIV0R: Clock Division Setting Register 0

Sets the division ratio for the clocks used for internal device operation.

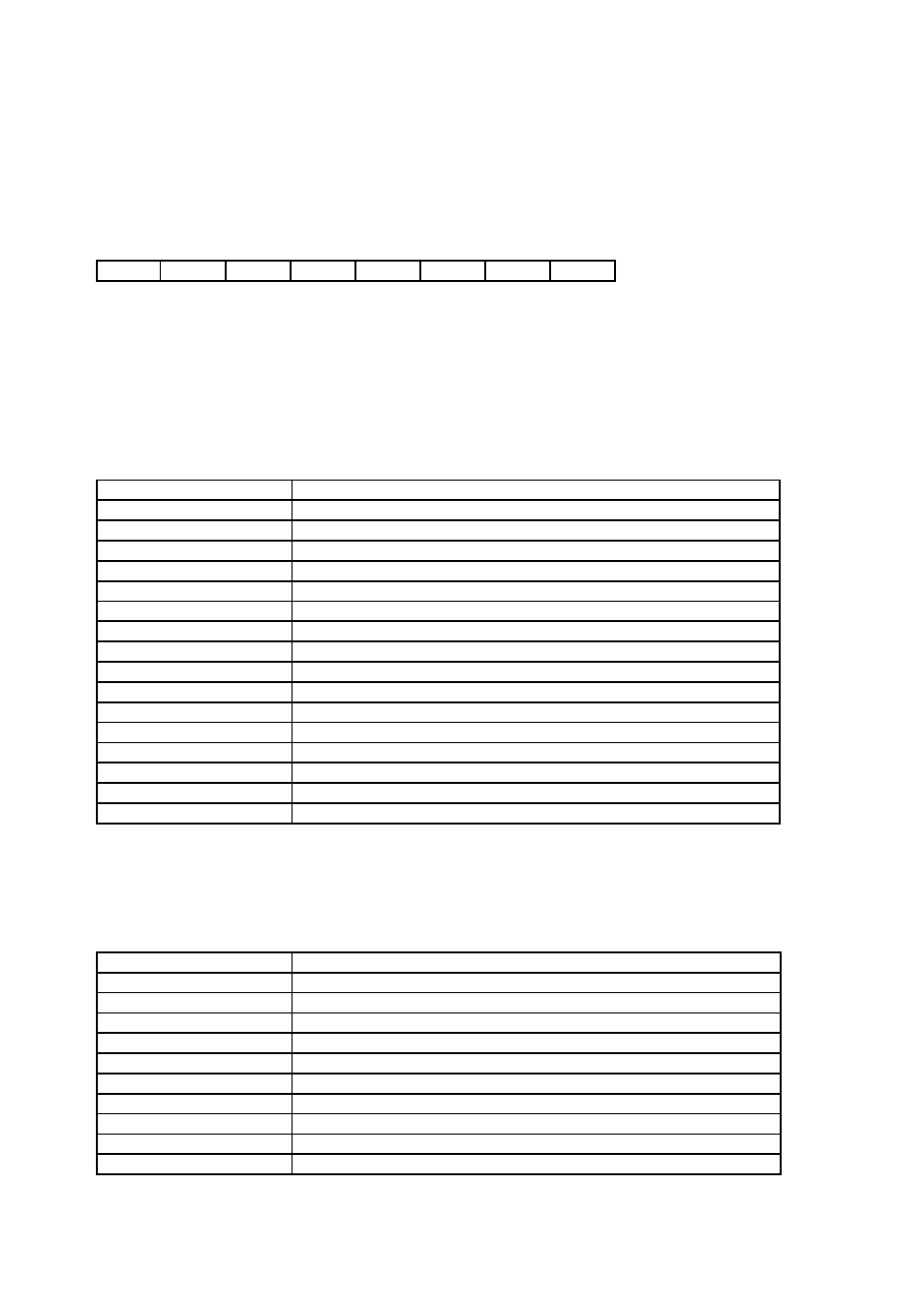

DIVR0: Address 0486h (Access: Byte, Half-word)

Meaning of Bit Attribute Symbols (Page No.10)

” for details of the attributes.)

• Sets up the clock for the CPU and internal buses (CLKB), and the clock for the peripheral circuits and

peripheral bus (CLKP).

• Bit7-4: CLKB division selection

• Do not change the division ratio with B3-B0 if current CLKB frequency is equal or above 80MHz !

• Sets the clock division ratio for the clock used by the CPU, internal memory, and internal buses (CLKB).

The 16 options listed in the table are available.

• Do not set a division ratio that exceeds the maximum operating frequency of the device.

• Bit3-0: CLKP division selection

7

6

5

4

3

2

1

0

bit

B3

B2

B1

B0

P3

P2

P1

P0

0

0

0

0

0

0

1

1

Initial value (

INIT pin input,

watchdog reset

)

X

X

X

X

X

X

X

X

Initial value

(software reset)

R/W

R/W

R/W

R/W

R/W

R/W

R/W

R/W

Attribute

B3-B0

CPU clock (CLKB) division ratio

0000

Φ/1 (initial value)

0001

Φ/2

0010

Φ/3

0011

Φ/4

0100

Φ/5

0101

Φ/6

0110

Φ/7

0111

Φ/8

1000

Φ/9

1001

Φ/10

1010

Φ/11

1011

Φ/12

1100

Φ/13

1101

Φ/14

1110

Φ/15

1111

Φ/16

P3-P0

Peripheral clock (CLKP) division ratio

0000

Φ/1

0001

Φ/2

0010

Φ/3

0011

Φ/4 (initial value)

0100

Φ/5

0101

Φ/6

0110

Φ/7

0111

Φ/8

1000

Φ/9

1001

Φ/10