FUJITSU MB91460 SERIES FR60 User Manual

Page 193

177

Chapter 11 Memory Controller

8.Explanations of Registers

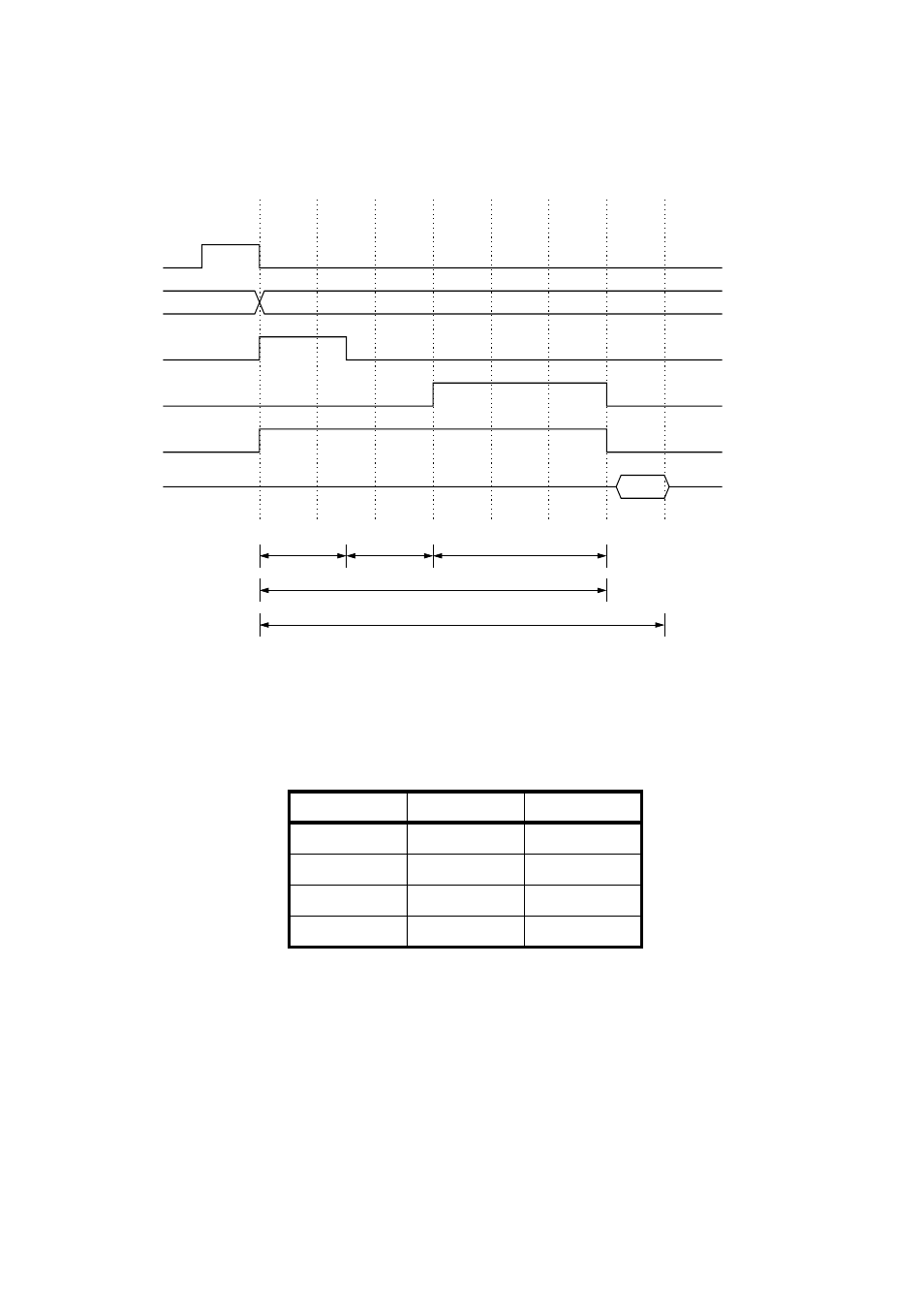

FLASH access cycle waveform

Figure

shows the example of a FLASH access cycle. In the FMWT register the three parts of the FLASH timing

tATD, tALEH, tEQ and tWTC can be configured independently. The table below lists the configuration values for

this example.

The resulting FLASH access cycle (tRC) time is 7 cycles (WTC+1).

• BIT[2:0]: PS[2:0] - Page size definition for Page Mode FLASH

PS is set to 0 after reset. Page Mode FLASH is disabled by default.

This setting defines the page size to 2^PS in number of bytes.

E.g. for Am29PL320D/MBM29PL3200 with a page size of 16 byte the value of PS has to be set to 4.

(Embedded FLASH memories on MB91460 series do not support page mode)

Symbol

Length

Setup

tATD

1.5 cycles

ATD=2

tALEH

1.5 cycles

ALEH=2

tEQ

3 cycles

EQ=5

tWTC

6 cycles

WTC=6

flash_start

FMA

ATDIN

EQIN

flash_wait

DO

tRC

tWTC

tATD

tEQ

tALEH

Figure 8-1 Timing of a FLASH access cycle

- XG Series P3NK-4452-01ENZD (614 pages)

- FPCAC14C (1 page)

- MCJ3230SS (161 pages)

- MBA3073NC (138 pages)

- T5140 (102 pages)

- T5140 (76 pages)

- MAM3367MC/MP (152 pages)

- MPC3045AH (185 pages)

- MB2142-02 (23 pages)

- MB15F86UL (6 pages)

- MHS2030AT (40 pages)

- MHW2100BS (296 pages)

- MHK2060AT (227 pages)

- Disk Drives MHK2060AT (227 pages)

- MCM3064SS (170 pages)

- Mainboard D1561 (45 pages)

- MHC2040AT (219 pages)

- D1961 (45 pages)

- DISK DRIVES MHM2100AT (231 pages)

- MHR2010AT (250 pages)

- MHZ2120BJ (320 pages)

- MCE3064AP (175 pages)

- LQFP-64P (16 pages)

- Solaris PCI GigabitEthernet 3.0 (115 pages)

- MAY2036RC (94 pages)

- MAB3091 (142 pages)

- MPE3XXXAT (191 pages)

- MHV2040AH (40 pages)

- MHW2040AC (278 pages)

- ETERNUSmgr P2X0-0202-01EN (64 pages)

- VSS Hardware Provider 2.1 (134 pages)

- MAG3182FC (61 pages)

- MAU3147NC/NP (130 pages)

- MAX3147RC (94 pages)

- MHV2160BT (296 pages)

- MHV2040AT (280 pages)

- MAW3300NC/NP (130 pages)

- DeskPower E623 (50 pages)

- MAG3182LC (133 pages)

- OPTICAL DISK DRIVES MDG3064UB (42 pages)

- MHF2021AT (225 pages)

- MHR2040AT (40 pages)

- Single Drive FTM7926FB (1 page)

- PG-FCS103 (98 pages)

- MAS3735FC (114 pages)