7 synchronous write enable output, Figure 5-6, Timing – FUJITSU MB91460 SERIES FR60 User Manual

Page 584

568

Chapter 31 External Bus

5.Operation of the Ordinary bus interface

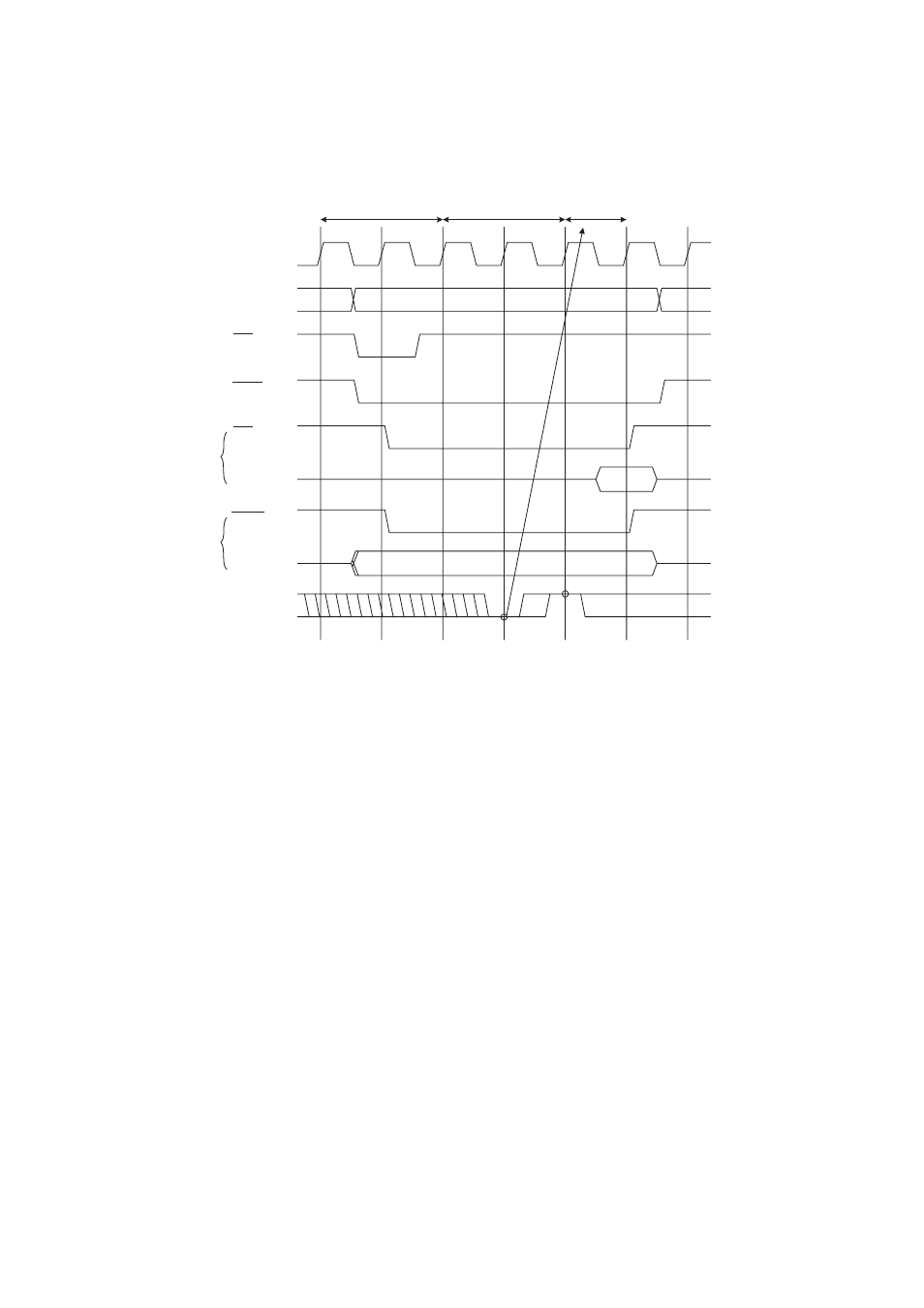

Figure 5-6 Timing Chart for the External Wait Cycle

Setting 1 for the TYP0 bit of the ACR register and enabling the external RDY input pin enables external wait

cycles to be inserted.

In Figure 4.5 - 6, the oblique - lined portion of the RDY pin is invalid because the wait based on the automatic wait

cycle remains in effect.

The value at the RDY input pin is evaluated from the last automatic wait cycle on.

Once a wait cycle is completed, the value at the PDY input pin remains invalid until the next access cycle is

started.

5.7 Synchronous Write Enable Output

This section shows the operation timing for synchronous write enable output.

■

Operation Timing for Synchronous Write Enable Output

"Timing Chart for Synchronous Write Enable Output" shows the operation timing for (TYP3-0=0000

B

,

AWR=0000

H

).

Basic cycle

2 auto-wait cycles Wait cycle by RDY

Wait

Release

MCLK

AS

CSn

RD

A[31:0]

D[31:0]

D[31:0]

WRn

RDY