FUJITSU MB91460 SERIES FR60 User Manual

Page 969

953

Chapter 49 Real-Time Clock

4.Registers

recommended that the Sub-Second register is updated while the ST bit is "0".

However, if this update is done immediately after an RTC second interrupt there should be enough time to

securely modify the registers until the next reload operation (next second interrupt) even if ST is not set to

"0" and the module is in operation.

When updating the registers by using the ST bit the following must be taken into account:

The new value is written into the registers with the rising edge of the RUN bit. This RUN bit is clocked by the

RTC clock (32 kHz, 100kHz or 4 MHz depending on device and mode). To make sure that the update is

done properly, write the new values into the registers, set ST to 0, wait for the RUN bit to go low and then

start the circuit again by setting ST to 1. RUN will go low at the second rising edge of the RTC clock after ST

has been set to 0. It will rise again at the half second rising edge of RTC clock after ST has been set to 1. If

this operation is to be done several times directly after each other, wait for RUN to go to high before setting

ST to low again.

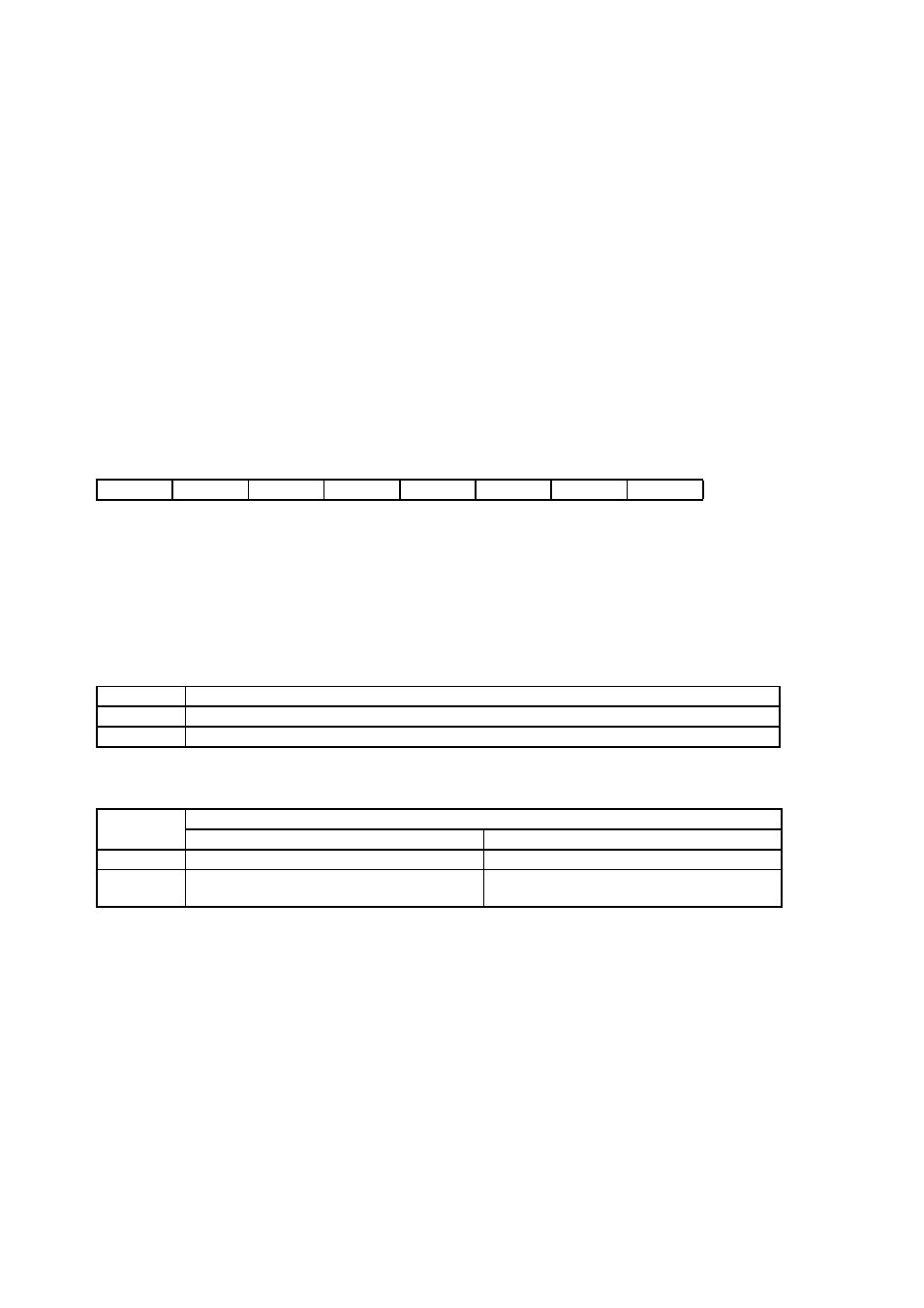

• WTCER: Address 04A1

H

(Access: Byte)

Meaning of Bit Attribute Symbols (Page No.10)

”.)

• bit7-2

:

Undefined

Writing does not affect the operation. The read value is indeterminate.

• bit1: Enable interrupt requests at half-second (500ms) intervals

When the hour counter overflows, this flag is set to “1”.

• bit0: half-second (500ms) interrupt request flag

7

6

5

4

3

2

1

0

bit

–

–

–

–

–

–

INTE4

INT4

–

–

–

–

–

–

0

0

Initial

value

–

–

–

–

–

–

0

0

When reset

RX/WX

RX/WX

RX/WX

RX/WX

RX/WX

RX/WX

R/W

R(R1),W

Attribute

INTE4

Operation

0

No interrupt requests

1

Generate interrupt requests at half-second (500 ms) intervals.

INT4

Status

Read

Write

0

No interrupt requests

Clear the flag.

1

Generate interrupt requests at half-second (500 ms)

intervals.

Writing does not affect the operation.