Q & a, 1 how do i enable or disable clock operation, 2 how do i select the main pll multiplier ratio – FUJITSU MB91460 SERIES FR60 User Manual

Page 218: 3 how do i select the operating clock source

202

Chapter 13 Clock Control

7.Q & A

7. Q & A

7.1 How do I enable or disable clock operation?

• There is no operation enable bit for the main clock. Main clock operation is always enabled.

(Halting the oscillation in subclock mode or stop mode is handled separately.)

• Main PLL operation is enabled by the main PLL operation enable bit (CLKR.PLL1EN).

Initially, the PLL is halted and therefore PLL operation must be enabled and the PLL started after setting the PLL

multiplier ratio.

• The subclock on the MB91460 does not halt and therefore no corresponding operation enable bit is

provided.

Instead, the subclock selection enable bit (CLKR.SCKEN) is used.

7.2 How do I select the main PLL multiplier ratio?

• The PLL multiplier can be set by using the PLL interface registers PLLDIVM and PLLDIVN (see chapter

).

7.3 How do I select the operating clock source?

Use the clock source selection bits (CLKR.CLKS[1:0]) to select main clock divided by 2, main PLL, or the

subclock as the operating clock source.

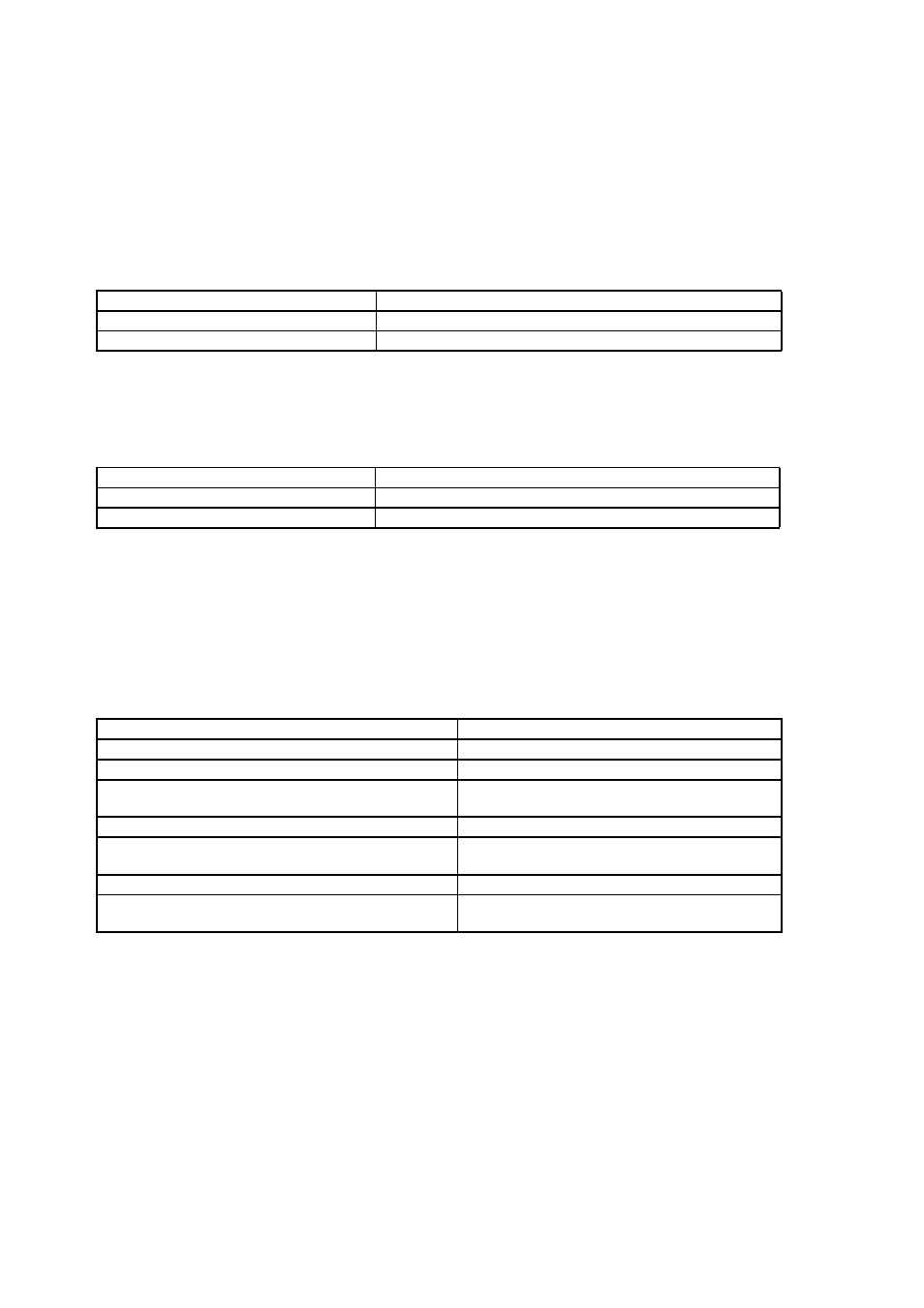

Operation

Main PLL operation enable bit (PLL1EN)

To halt the main PLL

Set to “0”.

To enable operation of the main PLL

Set to “1”.

Operation

Subclock selection enable bit (SCKEN)

Subclock selection prohibited

Set to “0”.

To enable selection of the subclock

Set to “1”.

Operating clock source

Clock source selection bits (CLKS[1:0])

To change from the initial value to the main clock divided by 2 Set initial values “00” or “01”.

To change from the initial value to the main PLL

Change from the initial values “00” to “10”.

To change from the initial value to the subclock

First change from the initial values “00” to “01”, and

then to “11”.

To change from the subclock to the main clock divided by 2

Change from “11” to “01”.

To change from the subclock to main PLL

First change from “11” to “01”, next set

“00”, and then set “10”.

To change from main PLL to the main clock divided by 2

Change from “10” to “00”.

To change from main PLL to the subclock

First change from “10” to “00”, next set

“01”, and then set “11”.