FUJITSU MB91460 SERIES FR60 User Manual

Page 434

418

Chapter 29 MPU / EDSU

4.Registers

•

operand address break,

•

data value break,

•

combined operand address and data value break and

•

memory protection violation.

Writing ’0’ resets the BD[31:0] bits to ’0’. Writing ’1’ to these bits is ignored. On a Read Modify Write instruction all

BD bits are read as ’1’.

BD1/BD0 setting at enabled address range function (also valid for the other pairs of BD bits in neighbourhood):

If the operand address range function is enabled with ER0 in addition to the point enables EP1 and EP0, then the

BD1 and BD0 detection bits are set in the following manner:

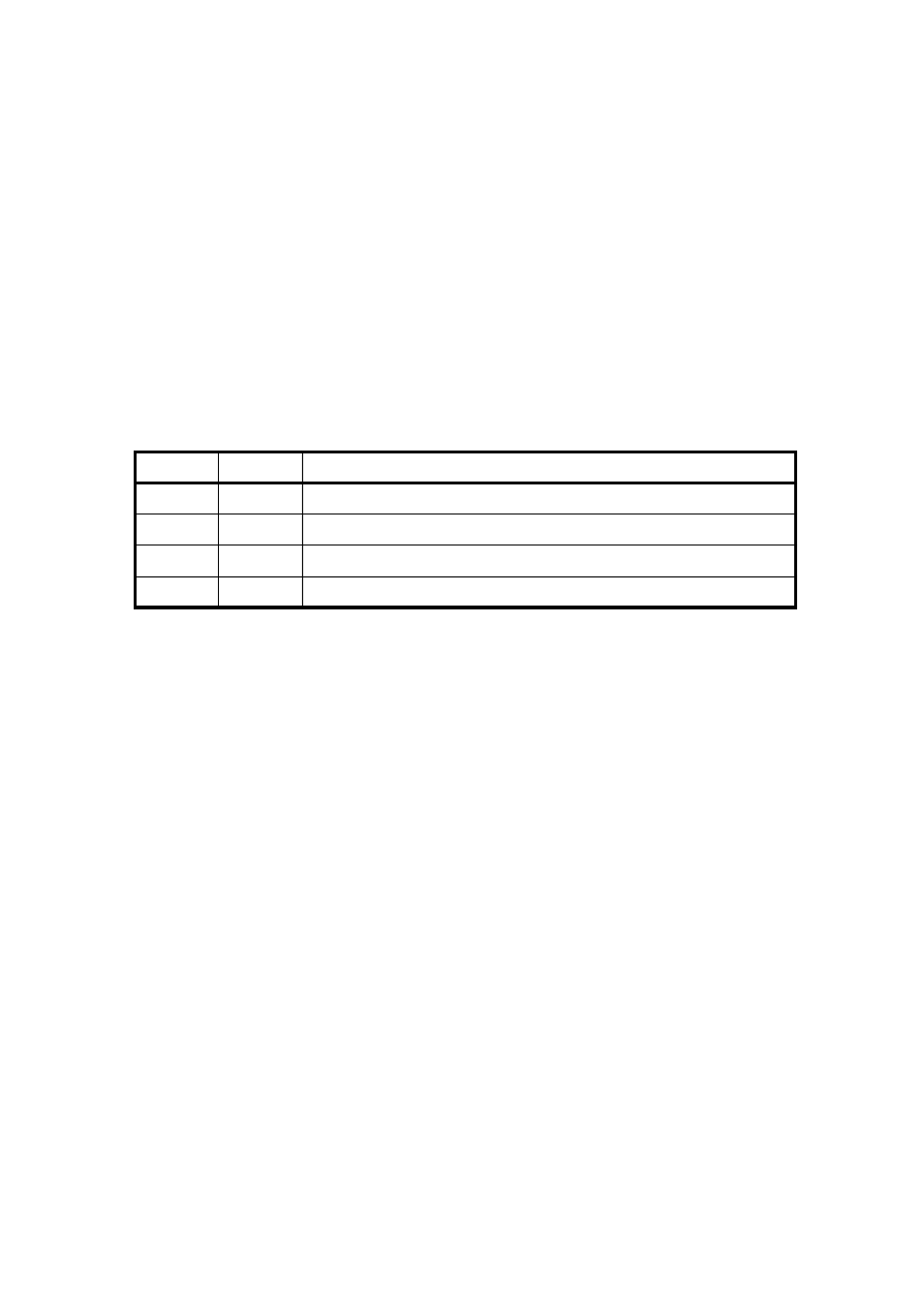

Table 4-2 BD Coding for Match on Start/Endoint or Range

BD1

BD0

Compare value: Instruction, Operand Address, Data Value

0

0

No match (Default)

0

1

Match on point (compare value == BAD0)

1

0

Match on point (compare value == BAD1)

1

1

Match on range (BAD0 < compare value < BAD1)

- XG Series P3NK-4452-01ENZD (614 pages)

- FPCAC14C (1 page)

- MCJ3230SS (161 pages)

- MBA3073NC (138 pages)

- T5140 (76 pages)

- T5140 (102 pages)

- MAM3367MC/MP (152 pages)

- MPC3045AH (185 pages)

- MB2142-02 (23 pages)

- MB15F86UL (6 pages)

- MHS2030AT (40 pages)

- MHW2100BS (296 pages)

- MHK2060AT (227 pages)

- Disk Drives MHK2060AT (227 pages)

- MCM3064SS (170 pages)

- Mainboard D1561 (45 pages)

- MHC2040AT (219 pages)

- D1961 (45 pages)

- DISK DRIVES MHM2100AT (231 pages)

- MHR2010AT (250 pages)

- MHZ2120BJ (320 pages)

- MCE3064AP (175 pages)

- LQFP-64P (16 pages)

- Solaris PCI GigabitEthernet 3.0 (115 pages)

- MAY2036RC (94 pages)

- MAB3091 (142 pages)

- MPE3XXXAT (191 pages)

- MHV2040AH (40 pages)

- MHW2040AC (278 pages)

- ETERNUSmgr P2X0-0202-01EN (64 pages)

- VSS Hardware Provider 2.1 (134 pages)

- MAG3182FC (61 pages)

- MAU3147NC/NP (130 pages)

- MAX3147RC (94 pages)

- MHV2160BT (296 pages)

- MHV2040AT (280 pages)

- MAW3300NC/NP (130 pages)

- DeskPower E623 (50 pages)

- MAG3182LC (133 pages)

- OPTICAL DISK DRIVES MDG3064UB (42 pages)

- MHF2021AT (225 pages)

- MHR2040AT (40 pages)

- Single Drive FTM7926FB (1 page)

- PG-FCS103 (98 pages)

- MAS3735FC (114 pages)