2 ics: input capture control register – FUJITSU MB91460 SERIES FR60 User Manual

Page 766

750

Chapter 36 Input Capture

4.Register

4.2 ICS: Input Capture Control Register

A register for controlling input capture

• ICS01 (Input capture 0-1): Address 0181h (Access:

Byte

)

• ICS23 (Input capture 2-3): Address 0183h (Access:

Byte

)

• ICS45 (Input capture 4-5): Address 02D1h (Access:

Byte

)

• ICS67 (Input capture 6-7): Address 02D3h (Access:

Byte

)

(For information on attributes, see “

Meaning of Bit Attribute Symbols (Page No.10)

• bit7: Input capture 1 interrupt request flag

• When the signal change (edge) selected by the active capture edge selection bit (EG[11:10]) is detected

on the input from an external pin, the flag becomes “1”.

• To activate the interrupt request it is necessary to set the interrupt enable bit (ICE1=“1”).

• If the timing of the interrupt request flag becoming “1” and the writing of “0” occur simultaneously, the

interrupt request flag will become “1”.

• bit6: Input capture 0 interrupt request flag

• When the signal change selected by the active capture edge selection bit (EG[01:00]) is detected on the

input from an external pin (CS0), the flag becomes “1”.

• To activate the interrupt request, the interrupt request permission setting (ICE1=“1”) is necessary.

• If the timing of the interrupt request flag becoming “1” and the writing of “0”occur simultaneously, the

interrupt request flag will become “1”.

• bit5: Input capture 1 interrupt request permission

• If input capture 1 interrupt request permission bit is set to “1”, input capture 1 interrupt request ICP1 will

be enabled.

• bit4: Input capture 0 interrupt request permission

• If input capture 0 interrupt request permission bit is set to “1”, input capture 0 interrupt request ICP0 will

be enabled.

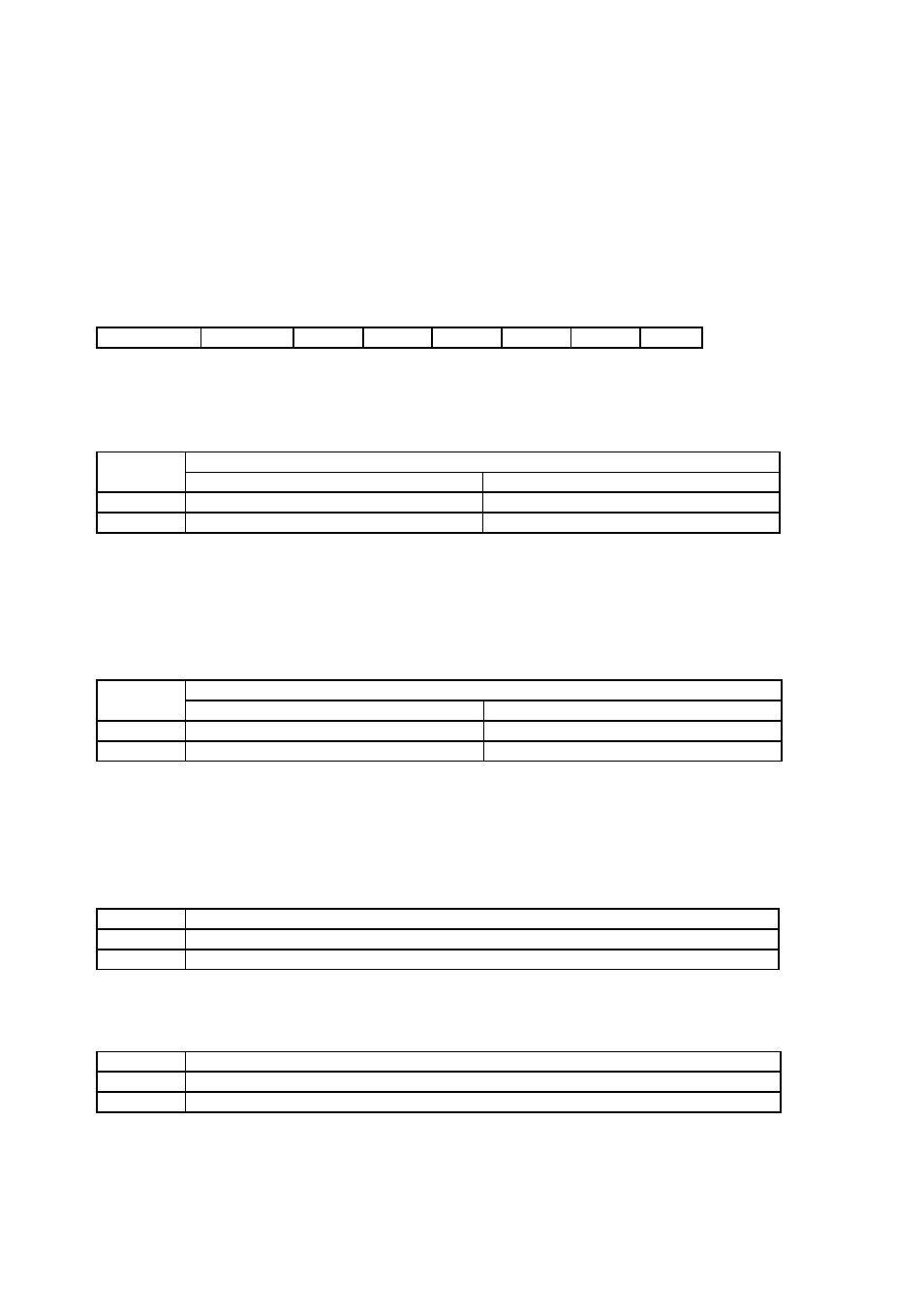

7

6

5

4

3

2

1

0

bit

ICP1

ICP0

ICE1

ICE0

EG11

EG10

EG01

EG00

0

0

0

0

0

0

0

0

Initial value

R(RM1),W

R(RM1),W

R/W

R/W

R/W

R/W

R/W

R/W

Attribute

ICP1

Status

Read

Write

0

No interrupt request

Clear flag

1

Interrupt request present (edge detection present)

No effect on operation

ICP0

Status

Read

Write

0

No interrupt request

Clear flag

1

Interrupt request present

No effect on operation

ICE1

Operation

0

Interrupt disabled

1

Interrupt enabled

ICE0

Operation

0

Interrupt disabled

1

Interrupt enabled