Configuration, Reload timer 0 (internal clock count), Reload timer 2 – FUJITSU MB91460 SERIES FR60 User Manual

Page 792: Ppg4, ppg5 reload timer 3, Ppg6, ppg7 reload timer 4, Ppg8, ppg9 reload timer 5, A/d), Figure 3-1 configuration diagram, Chapter 38 reload timer 3.configuration, Tmrlr0

776

Chapter 38 Reload Timer

3.Configuration

Reload timer 2

:

PPG4, PPG5

Reload timer 3

:

PPG6, PPG7

Reload timer 4

:

PPG8, PPG9

Reload timer 5

:

PPG10, PPG11

Reload timer 6

:

PPG12, PPG13

Reload timer 7

:

PPG14, PPG15

• A/D converter activation trigger source (Reload timer 7

:

A/D)

3. Configuration

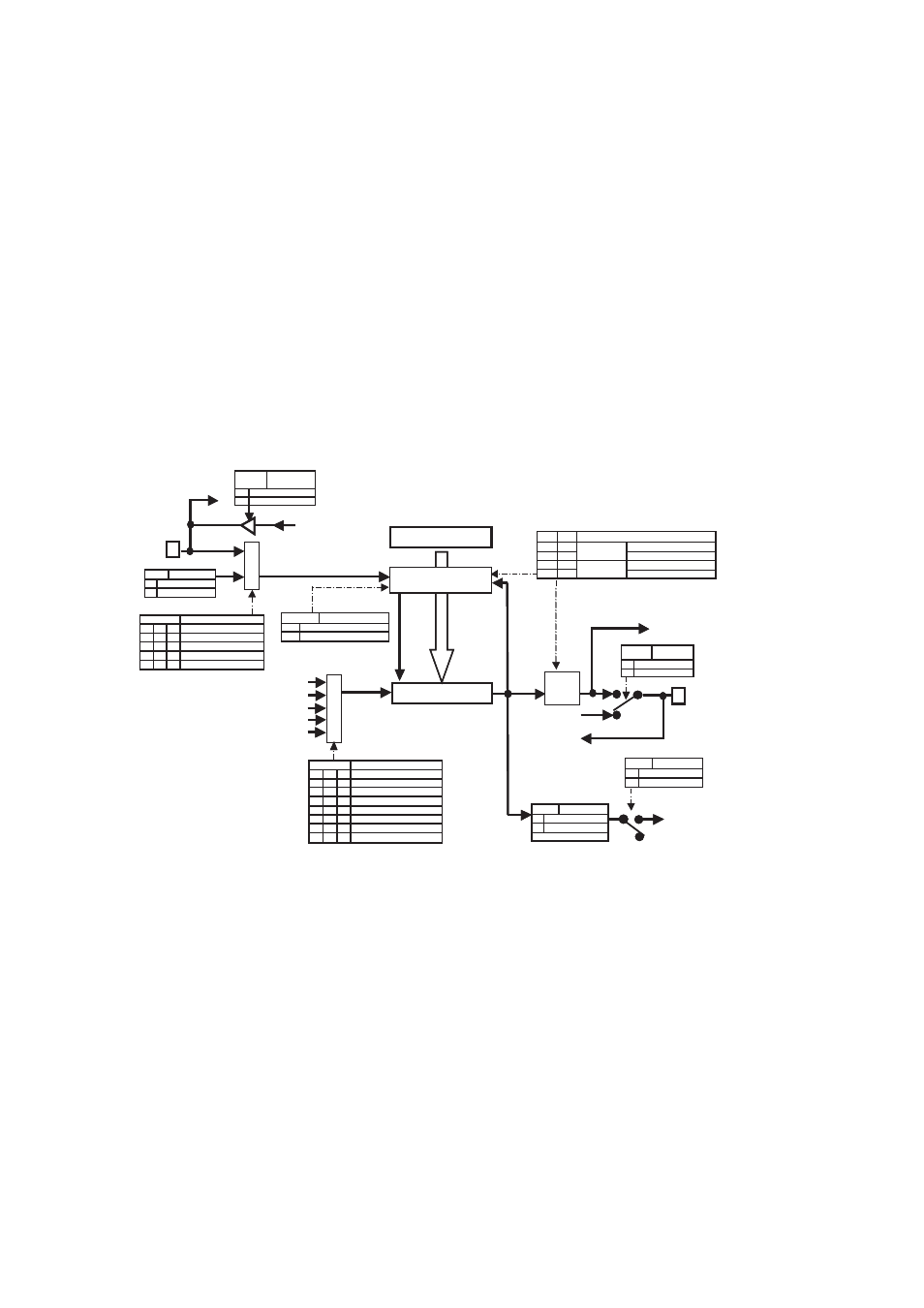

Figure 3-1 Configuration Diagram

CLKP /2

CLKP /2

3

CLKP /2

5

CLKP /2

6

CLKP /2

7

MOD2-0

0

0

1

1

0

1

1

0

0

0

0

0

X

X

1

TMCSRx: bit9-7

CNTE

TMCSRx:bit1

0

1

TRG TMCSRx:bit0

0

1

TMRLR0

16 bit reload register

16 bit down counter (=timer)

/

/

To general-purpose

port input

TIN0/ICU0/P14.0

Clock source

From general-purpose

port output

PFR14.0

0

1

Trigger selection

TMCSR:bit5, bit4

OUTL

0

0

RELD

1

0

1

1

0

* For external events, see the next chart.

TOT0

0

1

OCU0 output

TOT0 output

To general-purpose

port input

1

From general-purpose

port output

TO T0/OCU0/P15.0

0

INTE

TMCSRx:bit3

0

1

UF

TMCSRx:bit2

0

1

CSL2-0

0

0

1

1

0

1

1

0

0

0

0

0

0

1

1

CLKP/2

CLKP/2

3

CLKP /2

5

CLKP /2

6

TMCSRx: bit12-10

1

0

1

CLKP /2

7

0

0

1

1

1

Reload Timer 0 (Internal clock count)

Software trigger

External trigger rising edge

External trigger falling edge

External trigger both edges

Disabled

0

1

0

1

0

1

1

0

1

UF

Internal clock CLKP/2

Internal clock

Internal clock

(External event) *

Internal clock

Internal clock

Disabled

1

1

Disabled

0

.

Counter

activation

Stop

Reload/activation/stop

control circuit

Underflow

Reload

Latch,

output

change

Reload

Stop count (disable output)

Enable count

Selector

Selector

Stop

GP Port

Reload Timer Input

No effect

Soft trigger

Trigger (load + counter activation)

"H" square wave during count

"L" square wave during count

"L" toggle output on count start

"H" toggle output on count start

One-shot mode

Reload mode

Timer interrupt

(underflow)

Disable interrupts

Enable interrupts

Underflow not present

Underflow generation

WRITE 0: Flag clear

TIN0

Ch01 -> PPG0-PPG1

EPFR15.0

TMR0