15 reading from a fifo buffer, 16 handling of interrupts – FUJITSU MB91460 SERIES FR60 User Manual

Page 745

729

Chapter 34 CAN Controller

4.CAN Application

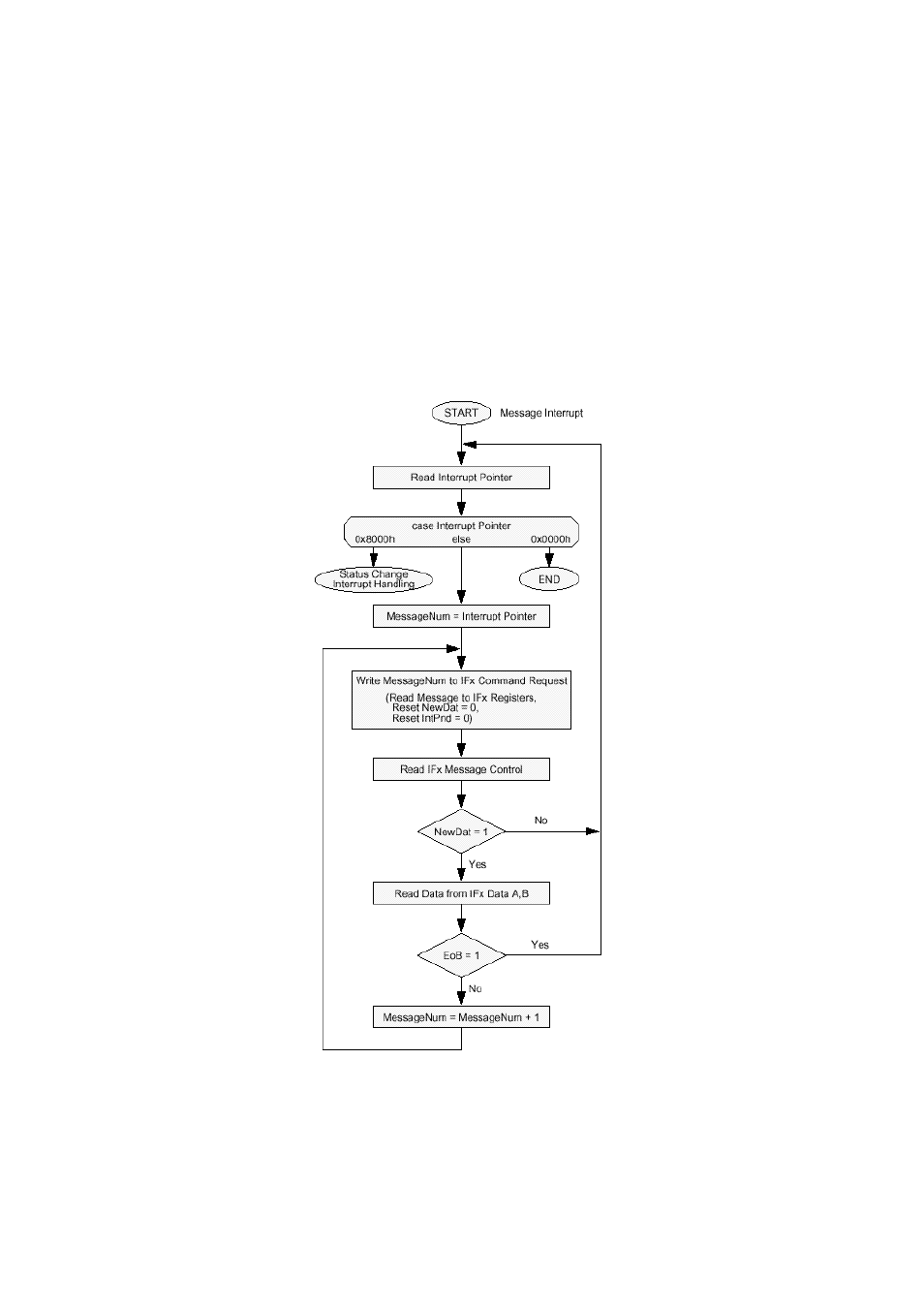

4.15 Reading from a FIFO Buffer

When the CPU transfers the contents of Message Object to the IFx Message Buffer registers by writing its

number to the IFx Command Request Register, the corresponding Command Mask Register should be

programmed the way that bits NewDat and IntPnd are reset to zero (TxRqst/NewDat = ‘1’ and ClrIntPnd =

‘1’). The values of these bits in the Message Control Register always reflect the status before resetting the

bits.

To assure the correct function of a FIFO Buffer, the CPU should read out the Message Objects starting at the

FIFO Object with the lowest message number.

shows how a set of Message Objects which are concatenated to a FIFO Buffer can be handled by

the CPU.

Figure 4-4 CPU Handling of a FIFO Buffer

4.16 Handling of Interrupts

If several interrupts are pending, the CAN Interrupt Register will point to the pending interrupt with the highest

priority, disregarding their chronological order. An interrupt remains pending until the CPU has cleared it.