FUJITSU MB91460 SERIES FR60 User Manual

Page 651

635

Chapter 32 USART (LIN / FIFO)

4.USART Registers

(Note)

The RX triggerlevel sets the reception FIFO level where the reception interrupt is activated. E.g. if

the triggerlevel is at its default value of RXL[3:0]=0000, the interrupt is activated if one reception is

stored in the FIFO. If the the triggerlevel is set to RXL[3:0]=1111, the interrupt is activated if 16

receptions are stored in the FIFO. In general: a reception interrupt is triggered if FSR[4:0] >

FCR[3:0].

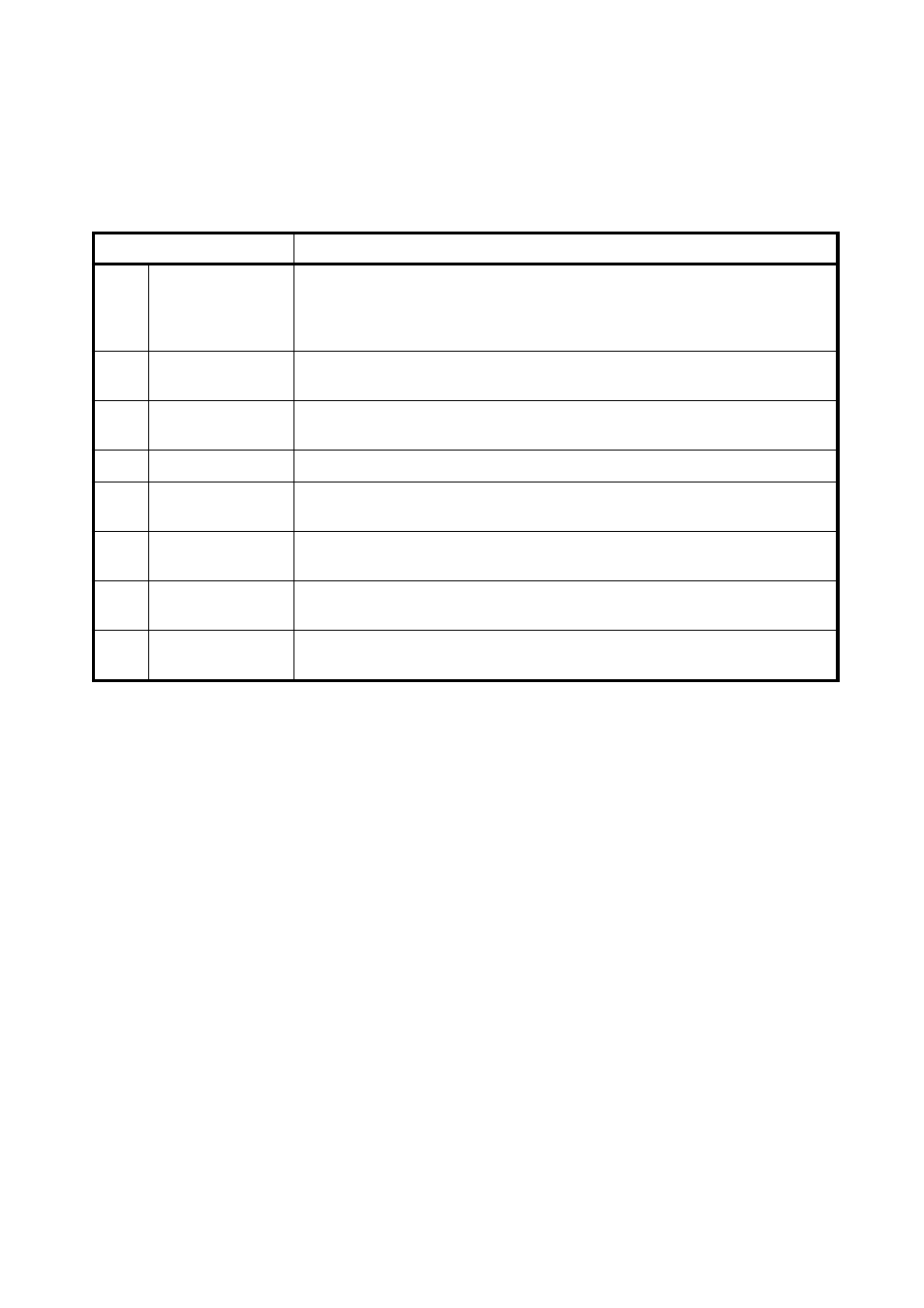

Table 4-9 Functions of each bit of fifo control register (FCR4)

Bit name

Function

bit 0

SVD: select Valid

Data Fifo read

• If this bit is set to 0 the fifo status register shows the number of valid data

from the RX fifo

• If this bit is set to 1 the fifo status register shows the number of valid data

from the TX fifo

bit 1

ETX: enable TX

fifo

• If this bit is set to 0 the TX fifo is disabled / fifo data is cleared

• If this bit is set to 1 the TX fifo is enabled.

bit 2

ERX: enable RX

fifo

• If this bit is set to 0 the RX fifo is disabled / fifo data is cleared

• If this bit is set to 1 the RX fifo is enabled.

bit 3

reserved

bit 4

RXL0: RX

Triggerlevel bit 0

• Set the triggerlevel of RX Interrupt

bit 5

RXL1: RX

Triggerlevel bit 1

• Set the triggerlevel of RX Interrupt

bit 6

RXL2: RX

Triggerlevel bit 2

• Set the triggerlevel of RX Interrupt

bit 7

RXL3: RX

Triggerlevel bit 3

• Set the triggerlevel of RX Interrupt