FUJITSU MB91460 SERIES FR60 User Manual

Page 753

737

Chapter 35 Free-Run Timer

4.Registers

• bit3: Clear mode

• Set the clear mode of the free-run timer.

• If the clear mode bit is set to “1”, when the count value of the free-run timer and the compare-register

value (OCCP) match, the count value of the free-run timer is cleared to “0000h”.

• The reset and writing “1” to the clear bit (CLR) cause to clear the count value of the free-run timer to

“0000h”, regardless of the setting of the clear mode bit.

• The count value of the free-run timer is only cleared when the free-run timer is running. When the free-

run timer is stopped, clear it by writing “0000h” to the timer data register (TCDT).

• bit2: Clear

• When the clear bit is set to “1”, the count value of the free-run timer is cleared to “0000h”. The clear bit is

read as “1” until the free-run timer is completely cleared.

When the free-run timer is completely cleared, the clear bit is also cleared to “0”.

• When the clear operation of the free-run timer and writing “1” to the clear bit occurs at the same time, the

clear bit keeps “1”, and after the next time the free-run timer is cleared, it is cleared.

• bit1-bit0: Count clock division ratio selection (when the internal clock is selected)

• Select the division ratio of the count clock of the free-run timer.

• Change the division ratio when the setting of the count clock division ratio selection bit is changed. When

the internal clock is selected as the count clock of the free-run timer (count clock selection bit ECLK=“0”),

change the setting when other peripheral modules (output compare, input capture, etc.) using the output

of the free-run timer are stopped.

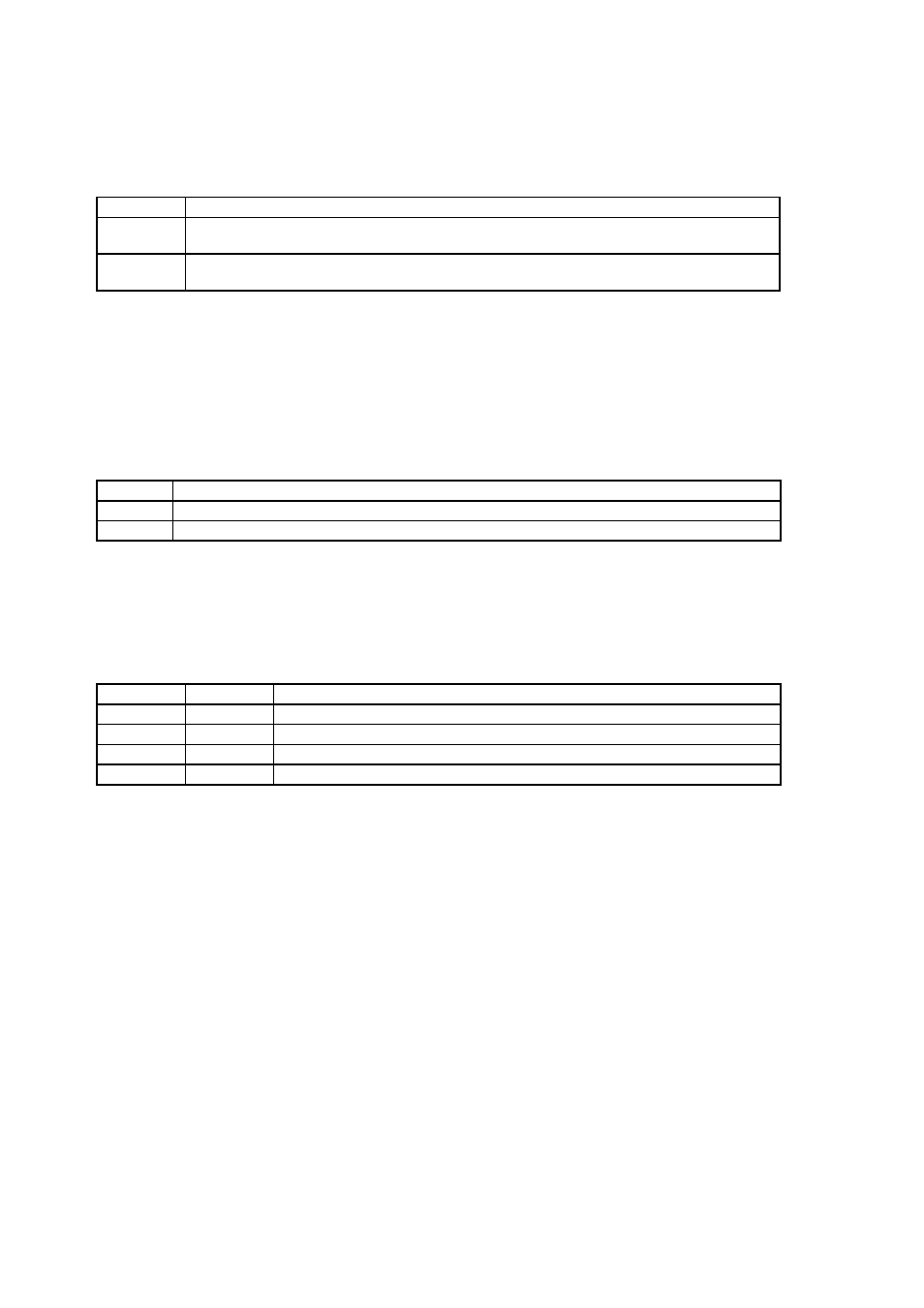

MODE

Clear mode

0

Clear the free-run timer by the reset and the clear bit (CLR).

1

Clear the free-run timer by the match with the reset, the clear bit (CLR), and the compare register value

of the output compare (OCCP).

CLR

Operation

0

No effect on operation

1

Clear the free-run timer.

CLK1

CLK0

The division ratio of the count clock

0

0

Peripheral clock (CLKP) divided by 4

0

1

Peripheral clock (CLKP) divided by 16

1

0

Peripheral clock (CLKP) divided by 32

1

1

Peripheral clock (CLKP) divided by 64