FUJITSU MB91460 SERIES FR60 User Manual

Page 25

9

Chapter 1 Introduction

4.How to Use This Document

■

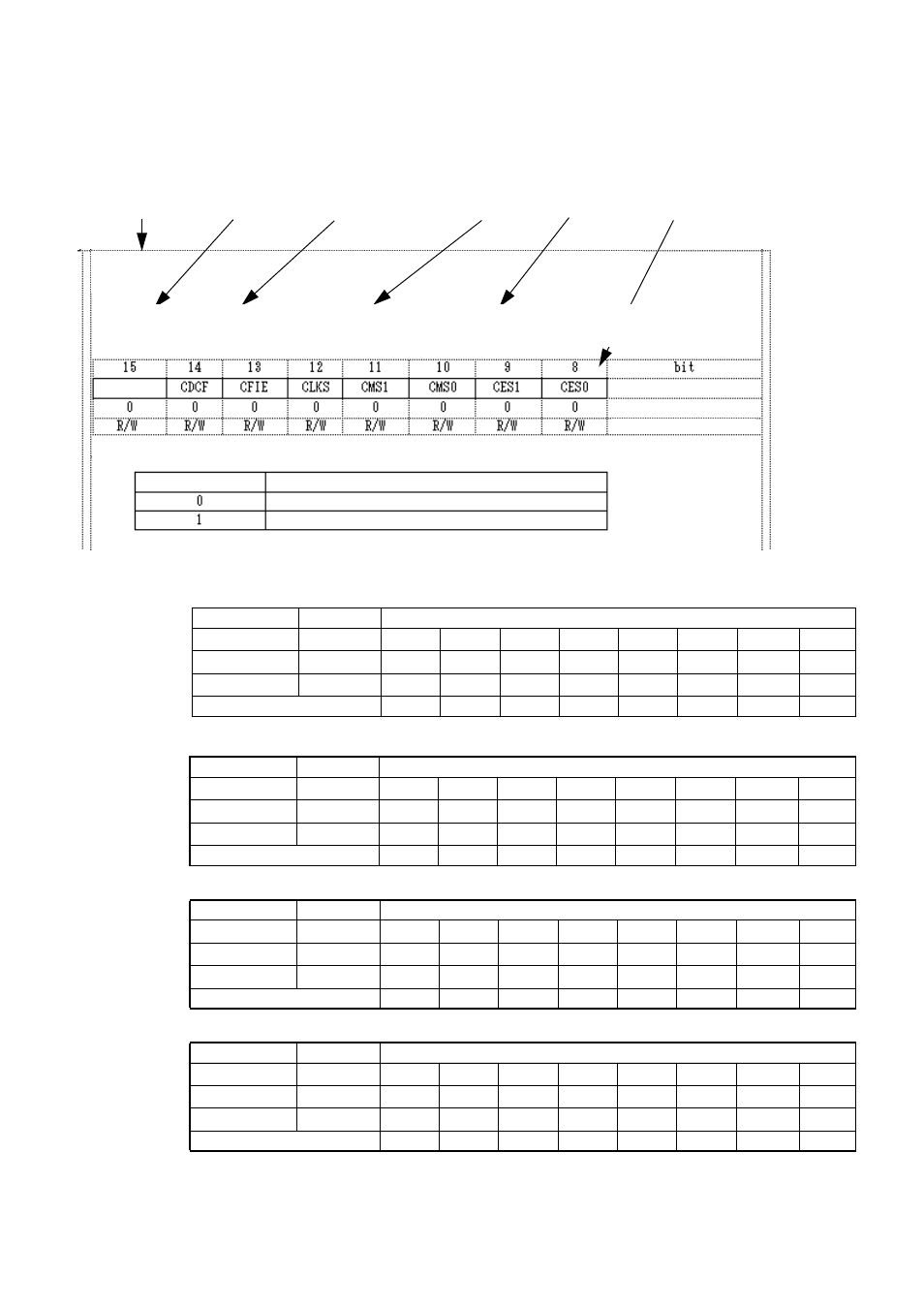

About access size and bit position

When access size changes, bit position changes.

• In the case that address offset value is +0 (Example: CCRH0 register)

• In the case that address offset value is +1 (Example: CCRL0 register)

• In the case that address offset value is +2 (Example: UDCR1 register)

• In the case that address offset value is +3 (Example: UDCR 1 register)

Access size

Address

Bit position

Byte

0B4

H

+0

H

07

06

05

04

03

02

01

00

Half-word

0B4

H

+0

H

15

14

13

12

11

10

09

08

Word

0B4

H

+0

H

31

30

29

28

27

26

25

24

Bit name

M16E

CDCF

CFIE

CLKS

CMS1

CMS0

CES1

CES0

Access size

Address

Bit position

Byte

0B4

H

+1

H

07

06

05

04

03

02

01

00

Half-word

0B4

H

+0

H

07

06

05

04

03

02

01

00

Word

0B4

H

+0

H

23

22

21

20

19

18

17

16

Bit name

Reserved

CTUT

UCRE

RLDE

UDCC

CGSC

CGE1

CGE0

Access size

Address

Bit position

Byte

0B0

H

+2

H

07

06

05

04

03

02

01

00

Half-word

0B0

H

+2

H

15

14

13

12

11

10

09

08

Word

0B0

H

+0

H

15

14

13

12

11

10

09

08

Bit name

D15

D14

D13

D12

D11

D10

D9

D8

Access size

Address

Bit position

Byte

0B0

H

+3

H

07

06

05

04

03

02

01

00

Half-word

0B0

H

+2

H

07

06

05

04

03

02

01

00

Word

0B0

H

+0

H

07

06

05

04

03

02

01

00

Bit name

D7

D6

D5

D4

D3

D2

D1

D0

Register mark

Register name

Target peripheral device Address

Access size

Bit position

(1) Counter control register (Higher byte)

This is the register (higher byte) which controls up/down counter operation.

CCRH0 (Up/down counter 0): address 00B4h (Access: Byte, Half-word, Word)

CCRH1 (Up/down counter 1): address 00B8h (Access: Byte, Half-word, Word)

M16E/Reserved

Initial value

Attribute

bit15: Enable 16-bit mode

M16E (CCRH0 only)

Enable 16-bit mode

8-bit x 2-channel mode (8-bit mode)

16-bit x 1-channel mode (16-bit mode)

*: CCRH1: ReservedAlways write 0 for writing. The read value is indeterminate.

*