For 2-cycle transfer – FUJITSU MB91460 SERIES FR60 User Manual

Page 385

369

Chapter 26 DMA Controller

3.DMA Controller (DMAC) Operation

■

Channel Group

The order of priority is set as shown in the following table.

3.12 Supplement on External Pin and Internal Operation Timing

This section provides supplementary information about external pins and internal operation tim-

ing.

■

Minimum Effective Pulse Width of the DREQ pin Input

Only channels 0-3 are applicable for the MB91460 series.

In all transfer modes for burst, step, block, and demand transfers, the minimum width required is five system

clock cycles (5 cycles of CLKT).

Note:

DACK output does not indicate acceptance of DREQ input. DREQ input is always accepted if DMA is enabled

but transfer has not started. Therefore, it is not necessary to retain DREQ input until DACK output is asserted

(except in demand transfer mode).

■

Negate Timing of the DREQ Pin Input when a Demand Transfer Request is Stopped

●

For 2-cycle transfer

For a demand transfer, be sure to set an address in an external area for the transfer source, the transfer

destination, or both.

•

If the transfer type is external <--> external: Negate before the last sense timing of the clock in the L section of

the external WRn pin output when accessing the transfer source for the last DMA transfer (section where

DACK = L and WRn = L). If DREQ is negated later than this, a DMA request may be sensed, resulting in

negation until the next transfer.

•

If the transfer type is external <--> internal: Negate before the last sense timing of the clock in the L section of

the external RD pin output when accessing the transfer source for the last DMA transfer (Section where DACK

= L and RD = L). If DREQ is negated later than this, a DMA request may be sensed, resulting in negation until

the next transfer

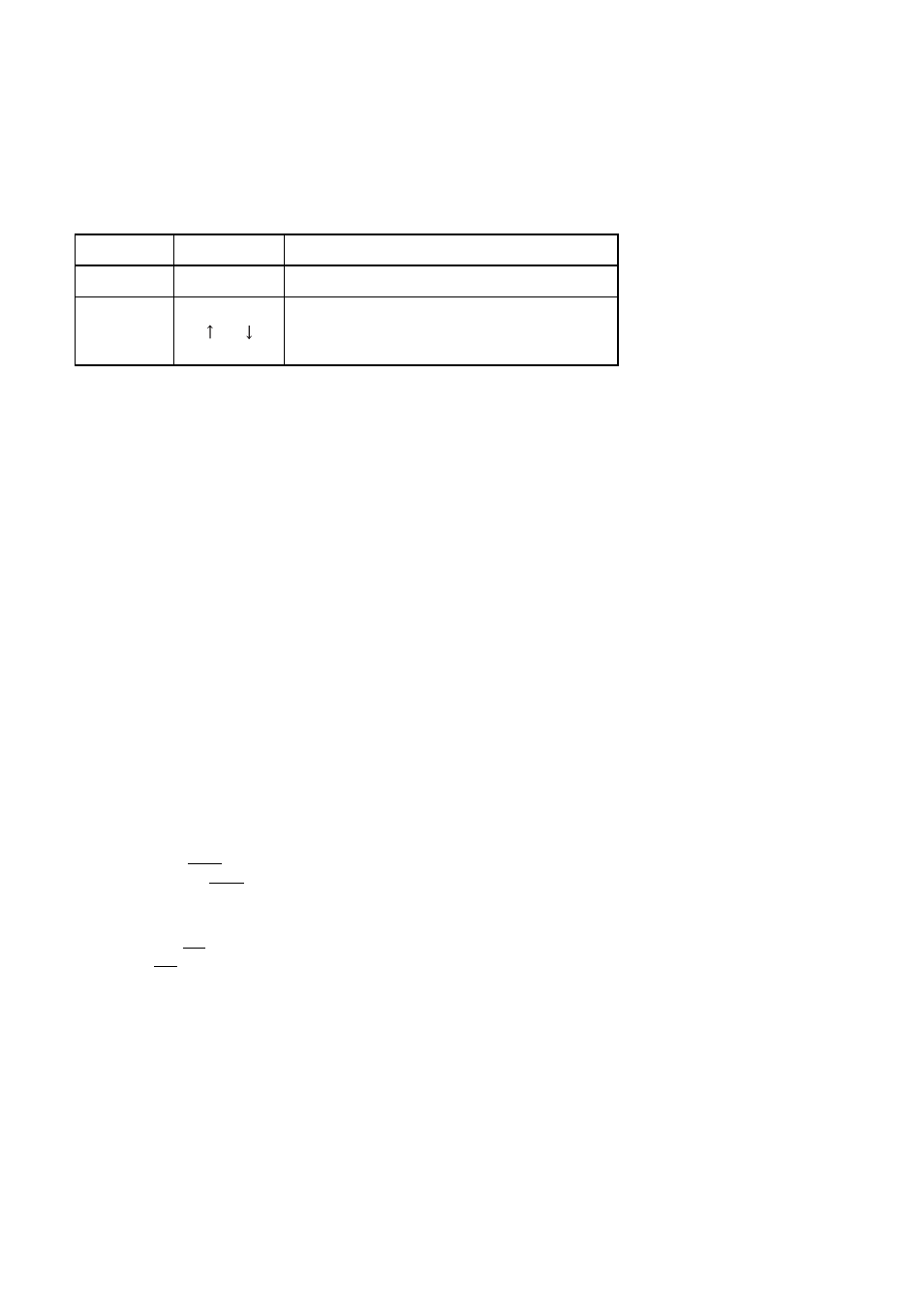

MODE

Priority

Remarks

Fixed

ch0 > ch1

−

Rotation

The initial state is the top row.

If transfer occurs for the top row, the priority

is reversed.

ch0 > ch1

ch0 < ch1