2 a/d control status register (adcs) – FUJITSU MB91460 SERIES FR60 User Manual

Page 906

890

Chapter 44 A/D Converter

3.Registers of A/D Converter

3.2 A/D Control Status Register (ADCS)

A/D control status register controls and shows the status of A/D converter. Do not overwrite ADCS0 register

during A/D converting.

■

A/D control status register 1 (ADCS1)

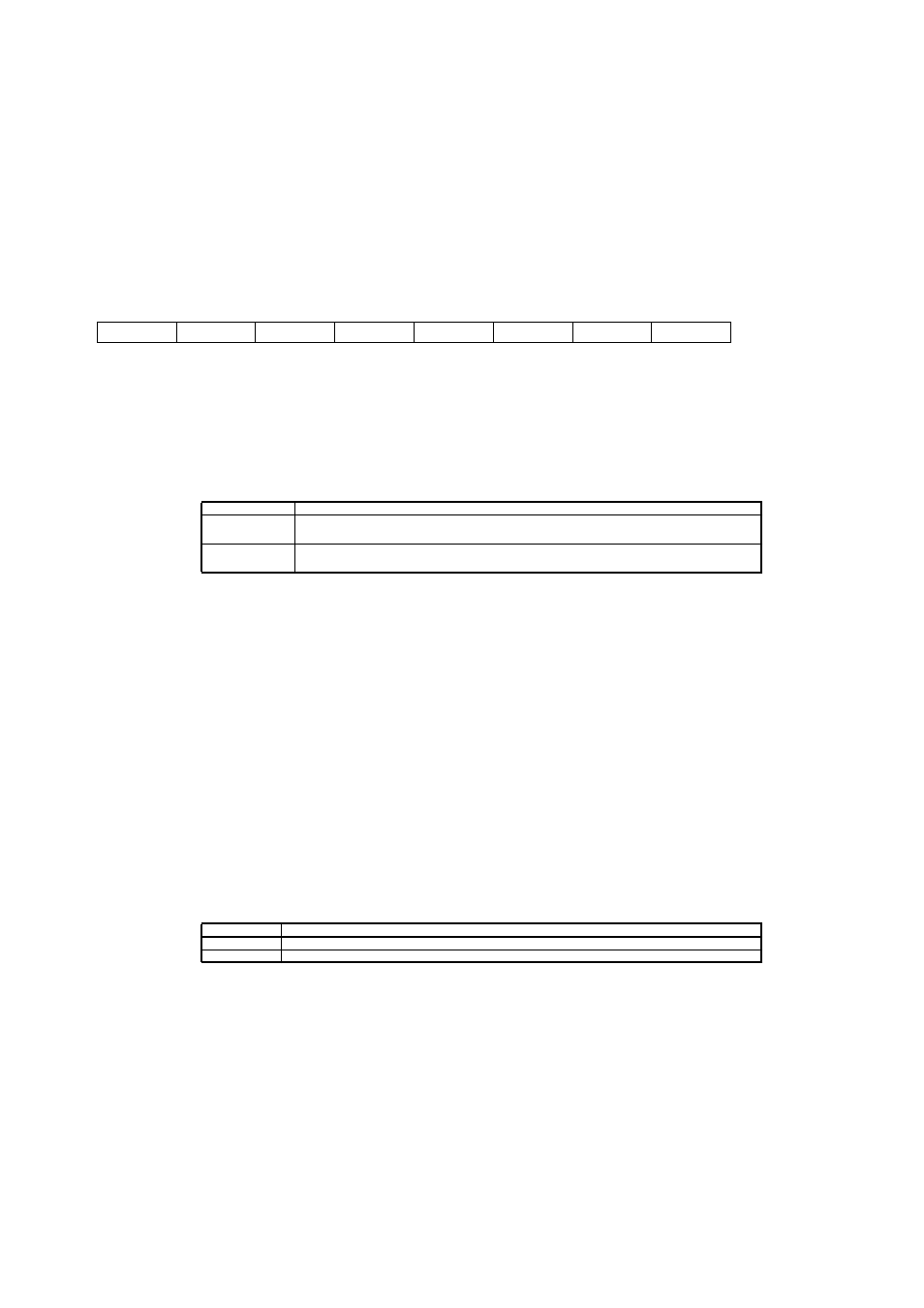

• ADCS1 (ADC0): Address 01A4h (Access:

Half-word, Byte

)

Meaning of Bit Attribute Symbols (Page No.10)

” for details of the attributes.)

[bit 7] BUSY (busy flag and stop)

RMW instructions read the bit as "1".

Cleared on the completion of A/D conversion in single conversion mode.

In continuous and stop mode, the flag is not cleared until conversion is terminated by writing "0".

Initialized to "0" by a reset.

Do not specify forcible termination and software activation (BUSY="0" and STRT="1") at the same time.

[bit 6] INT (interrupt)

This bit is set when conversion data is stored in ADCR.

If bit 5 (INTE) is "1" when this bit is set, an interrupt request is generated or, if activation of DMA is

enabled, DMA is activated.

Only clear this bit by writing "0" when A/D conversion is halted.

Initialized to "0" by a reset.

If DMA is used, this bit is cleared at the end of DMA transfer.

[bit 5] INTE (Interrupt enable)

This bit is enables or disables the conversion completion interrupt.

Cleared by a reset.

[bit 4] PAUS (A/D converter pause)

This bit is set when A/D conversion temporarily halts.

The A/D converter has only one register to store the conversion result. Therefore, the previous

conversion result is lost if it is not transferred by DMA when performing continuous conversion.

To avoid this problem, the next conversion data is not stored in the data register until the previous value

has been transferred by DMA. A/D conversion halts during this time. A/D conversion restarts when

using DMA.

This bit is only meaningful when using DMA.

15

14

13

12

11

10

9

8

Bit

BUSY

INT

INTE

PAUS

STS1

STS0

STRT

reserved

0

0

0

0

0

0

0

0

Initial

value

R/W

R/W

R/W

R/W

R/W

R/W

R/W

R/W

Attribute

BUSY

Function

Reading

A/D converter operation indication bit. Set on activation of A/D conversion

and cleared on completion.

Writing

Writing "0" to this bit during A/D conversion forcibly terminates

conversion. Use to forcibly terminate in continuous and stop modes.

INTE

Function

0

Disable interrupt [Initial value]

1

Enable interrupt