3 ten bit slave address register (itba0) – FUJITSU MB91460 SERIES FR60 User Manual

Page 692

676

Chapter 33 I2C Controller

2.I2C Interface Registers

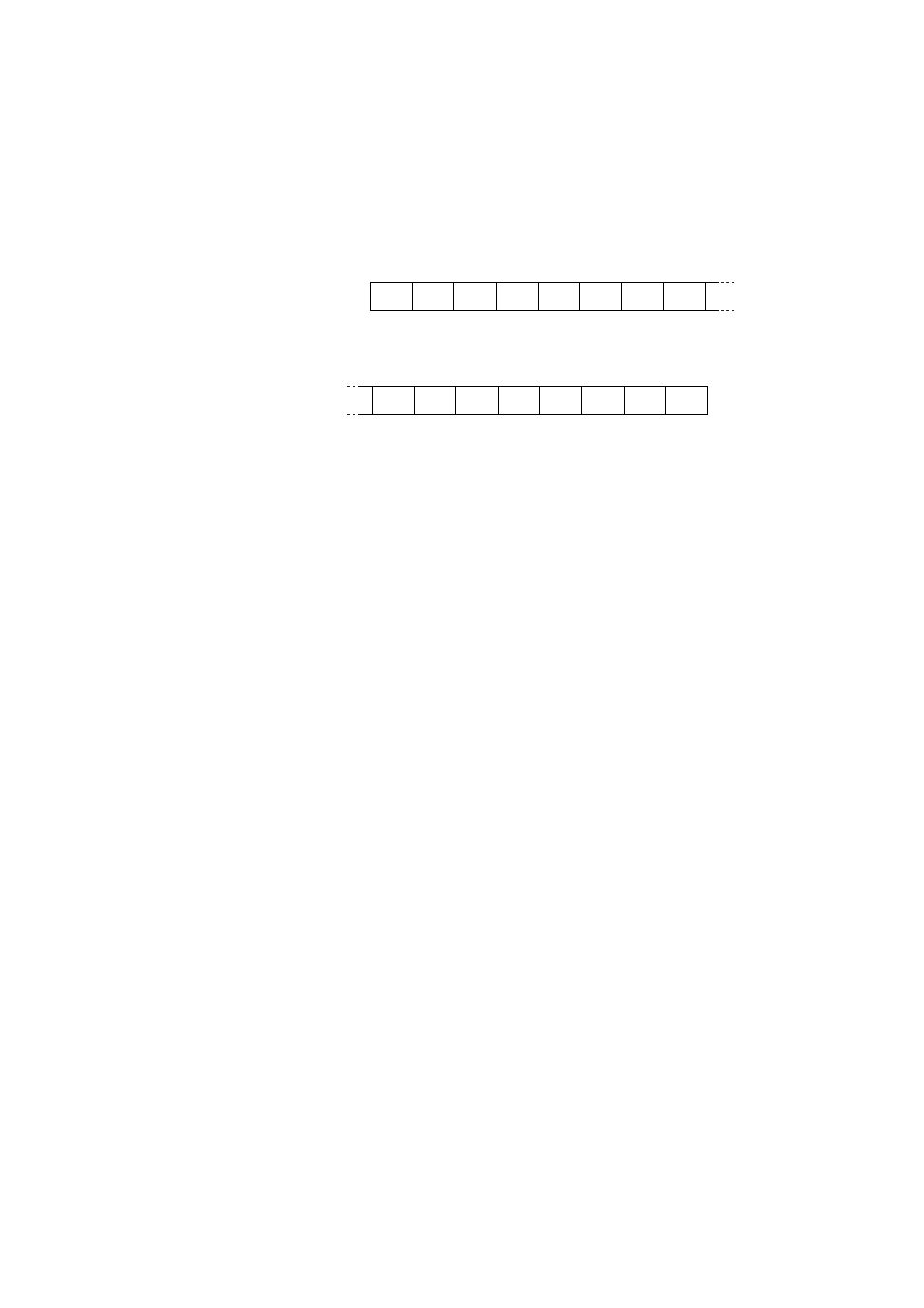

2.3 Ten Bit Slave Address Register (ITBA0)

This register (ITBAH0 / ITBAL0) designates the ten bit slave address.

Write access to this register is only possible if the interface is disabled (EN=‘0’ in ICCR0).

[bit 15] - [bit 10] Not used.

These bits always read ‘0’.

[bit 9] - [bit 0] TBA - Ten Bit slave Address (TA9-TA0)

When address data is received in slave mode, it is compared to the ITBA0 register if the ten bit address is

enabled (ENTB=‘1’ in the ITMK0 register). An acknowledge is sent to the master after reception of a ten bit

address header with write access

1

. Then, the second incoming byte is compared to the ITBA0 register. If a

match is detected, an acknowledge signal is sent to the master device and the AAS bit is set.

Additionally, the interface acknowledges upon the the reception of a ten bit header with read access

2

after a

repeated start conditon.

All bits of the slave address may be masked using the ITMK0 register. The received ten bit slave address is

written back to the ITBA0 register, it is only valid while the AAS bit in the IBSR0 register is ‘1’.

1.

Note: a ten bit header (write access) consists of the following bit sequence: 11110, TA9, TA8, 0.

2.

Note: a ten bit header (read access) consists of the following bit sequence: 11110, TA9, TA8, 1.

---

---

---

---

---

---

TA9

TA8

⇐

Bit no.

Read/write

⇒

(-)

(-)

(-)

(-)

(-)

(-)

(R/W) (R/W)

Default value

⇒

(0)

(0)

(0)

(0)

(0)

(0)

(0)

(0)

Ten Bit Address high byte

Address : 0000D2

H

15

14

13

12

11

10

9

8

ITBAH0

TA7

TA6

TA5

TA4

TA3

TA2

TA1

TA0

⇐

Bit no.

Read/write

⇒

(R/W) (R/W) (R/W) (R/W) (R/W) (R/W) (R/W) (R/W)

Default value

⇒

(0)

(0)

(0)

(0)

(0)

(0)

(0)

(0)

Address : 0000D3

H

7

6

5

4

3

2

1

0

ITBAL0

Ten Bit Address low byte