8 csn delay setting – FUJITSU MB91460 SERIES FR60 User Manual

Page 586

570

Chapter 31 External Bus

5.Operation of the Ordinary bus interface

•

If synchronous write enable output is used, the following restrictions apply:

Do not set the following additional wait because the timing for synchronous write enable output becomes

meaningless:

- CS -> RD/WRn setup (Always write 0 to the W01 bit of AWR)

- First wait cycle setting (Always write 0000 to bits W15-W12 of AWR)

Do not set the following access types (TYPE3-0 bits (Bits 3-0) in the ACR register) because the timing for

synchronous write enable output becomes meaningless:

- Multiplex bus setting (Always write 0 to the TYPE2 bit of ACR)

- RDY input enable setting (Always write 0 to the TYPE0 bit of ACR)

Always set the burst length to "1" (BST1 to 0 bit = 0) for the synchronous write enable output

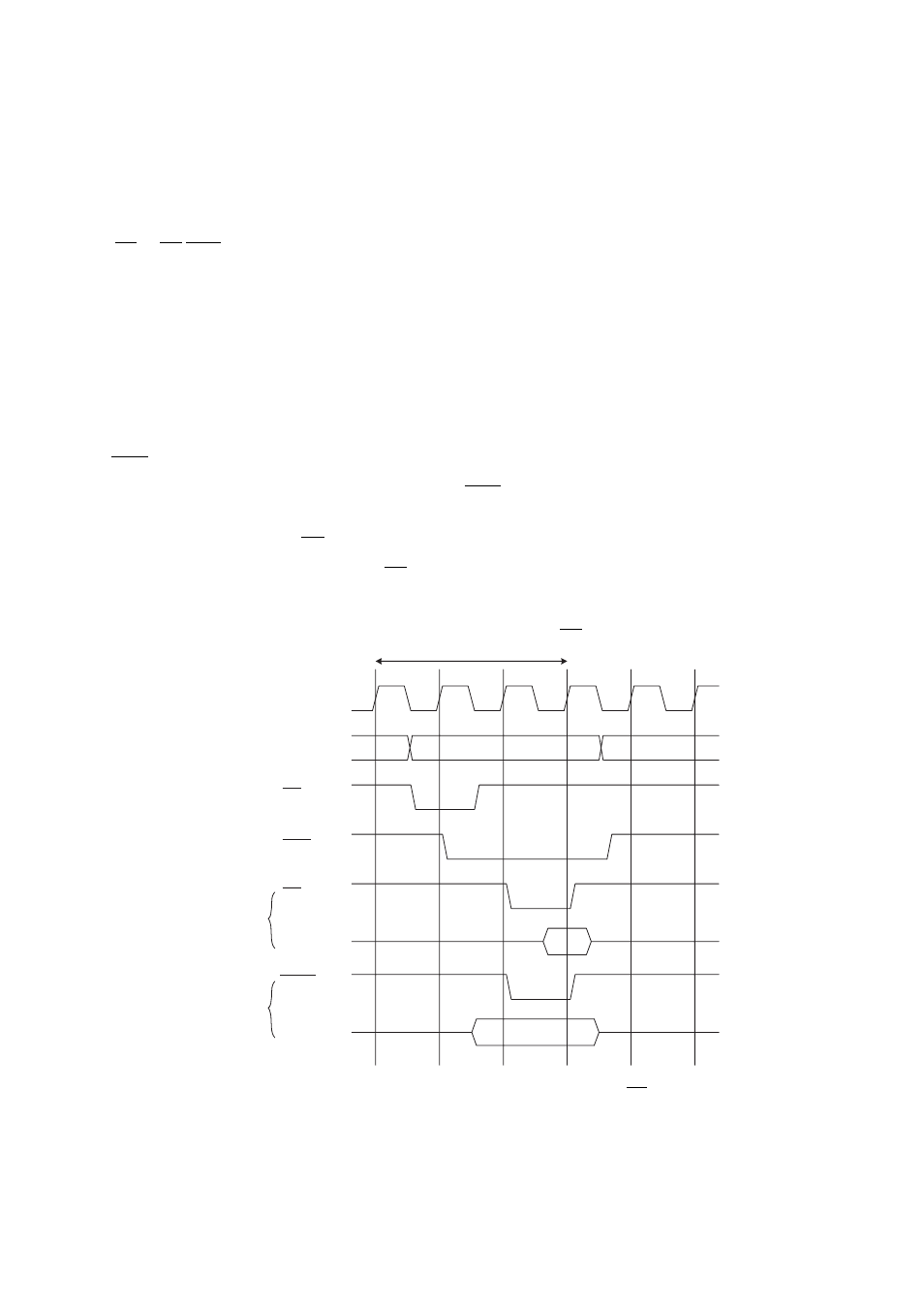

5.8 CSn Delay Setting

This section shows the operation timing for the CSn delay setting.

■

Operation Timing for the CS Delay Setting

"Operation Timing Chart for the CS Delay Setting" shows the operation timing for (TYP3-0=0000

B

,

AWR=000C

H

).

Figure 5-8 Operation Timing Chart for the CS Delay Setting

If the W02 bit is 1, assertion starts in the cycle following the cycle in which AS is asserted. For successive

accesses, a negation period is inserted.

READ

WRITE

MCLK

AS

CSn

RD

D[31:0]

WRn

D[31:0]

A[31:0]