Multiple eit processing – FUJITSU MB91460 SERIES FR60 User Manual

Page 139

123

Chapter 6 EIT: Exceptions, Interrupts and Traps

7.Multiple EIT Processing

7. Multiple EIT Processing

If multiple EITs are generated at the same time, CPU repeats the operation which selects one of the EIT to

accept, and then executes EIT sequence, and detects EIT again. If there is no EIT to accept upon detecting

EIT, CPU executes instruction of the last accepted EIT handler. Therefore, if multiple EITs are generated at

the same time, execution sequence of each EIT handler is determined by the following two parameters.

■

Priority Level of Receipt of EIT Triggers

Priority level of receipt of EIT triggers means the sequence to select which EIT triggers to execute by saving

PS and PC in order to update PC and masking other triggers where appropriate.

EIT does not always mean first-in first-out handler.

■

How to Mask Other Triggers upon the Receipt

Table below shows the execution sequence of each handler for multiple EIT triggers generated at the same

time when considering mask processes for other triggers upon the receipt of EIT triggers.

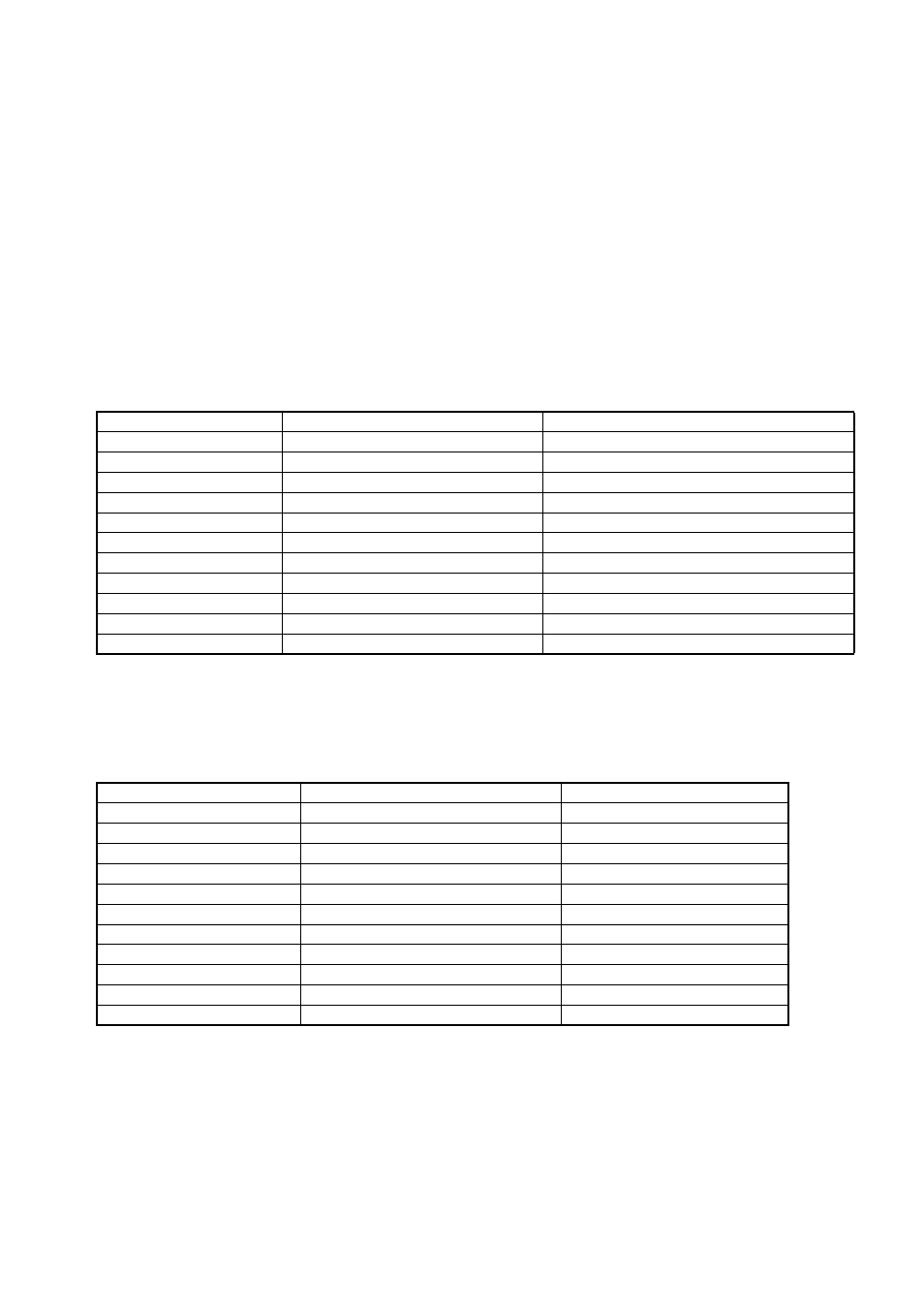

Table 7-1 Priority Level of Receipt of EIT Triggers and Mask for Other Triggers

Priority for accepting EITs

EIT

Masking of other EITs

1

Reset

All EITs are cleared

2

Instruction Break

Other EITs are canceled (ILM = 4)

3

INTE instruction

Other EITs are canceled (ILM = 4)

4

Undefined instruction exception

Other EITs are canceled (I-flag = 0)

5

INT instruction / Coprocessor exceptions I-flag = 0

6

Memory protection violation

I-flag = 0

7

User interrupt

ILM = level of accepted INT

8

NMI (user)

ILM = 15

9

NMI (emulator)

Other EITs are canceled (ILM = 4)

10

Step Trace trap

Other EITs are canceled (ILM = 4)

11

Operand Break

Other EITs are canceled (ILM = 4)

Table 7-2 Execution Sequence of EIT Handlers

Handler execution Priority

EIT

Masking of other EITs

1

Reset

All EITs are cleared

2

Undefined instruction exception

Other EITs are canceled (I-flag = 0)

3

Instruction Break

Other EITs are canceled (ILM = 4)

4

INTE instruction

Other EITs are canceled (ILM = 4)

5

NMI (emulator)

Other EITs are canceled (ILM = 4)

6

Step Trace trap

Other EITs are canceled (ILM = 4)

7

Operand Break

Other EITs are canceled (ILM = 4)

8

NMI (user)

ILM = 15

9

Memory protection violation

I-flag = 0

10

INT instruction / Coprocessor exceptions I-flag = 0

11

User interrupt

ILM = level of accepted INT