FUJITSU MB91460 SERIES FR60 User Manual

Page 225

209

Chapter 14 PLL Interface

4.Registers

Meaning of Bit Attribute Symbols (Page No.10)

” for details of the attributes.)

• Bit7-6: Reserved bits.The read value is always “0”.

• Bit5-0: PLL divide-by-N selection

(Note)

The register value can not be changed once PLL is selected as clock source (CLKS[1:0]=”10”).

(Note)

It is strongly recommended to disable the PLL (CLKR.PLL1EN=0) while or after changing the

PLLDIVM and PLLDIVN registers and to enable the PLL (CLKR.PLL1EN=1) afterwards.

• PLLDIVG: Address 048Eh (Access: Byte, Halfword, Word)

Meaning of Bit Attribute Symbols (Page No.10)

” for details of the attributes.)

• Bit7-4: Reserved bits.Always write “0” to these bits.

• Bit3-0: PLL auto gear start/end divide-by-G selection

(Note)

See chapter

for detailed information on how to use this function.

(Note)

Even though it is possible to select an odd division ratio (:3, :5, :7, etc.) for the divide-by-G counter it

is not recommended. Always select an even division ratio (:2, :4, :6, etc.).

(Note)

The register value can not be changed once PLL is selected as clock source (CLKS[1:0]=”10”).

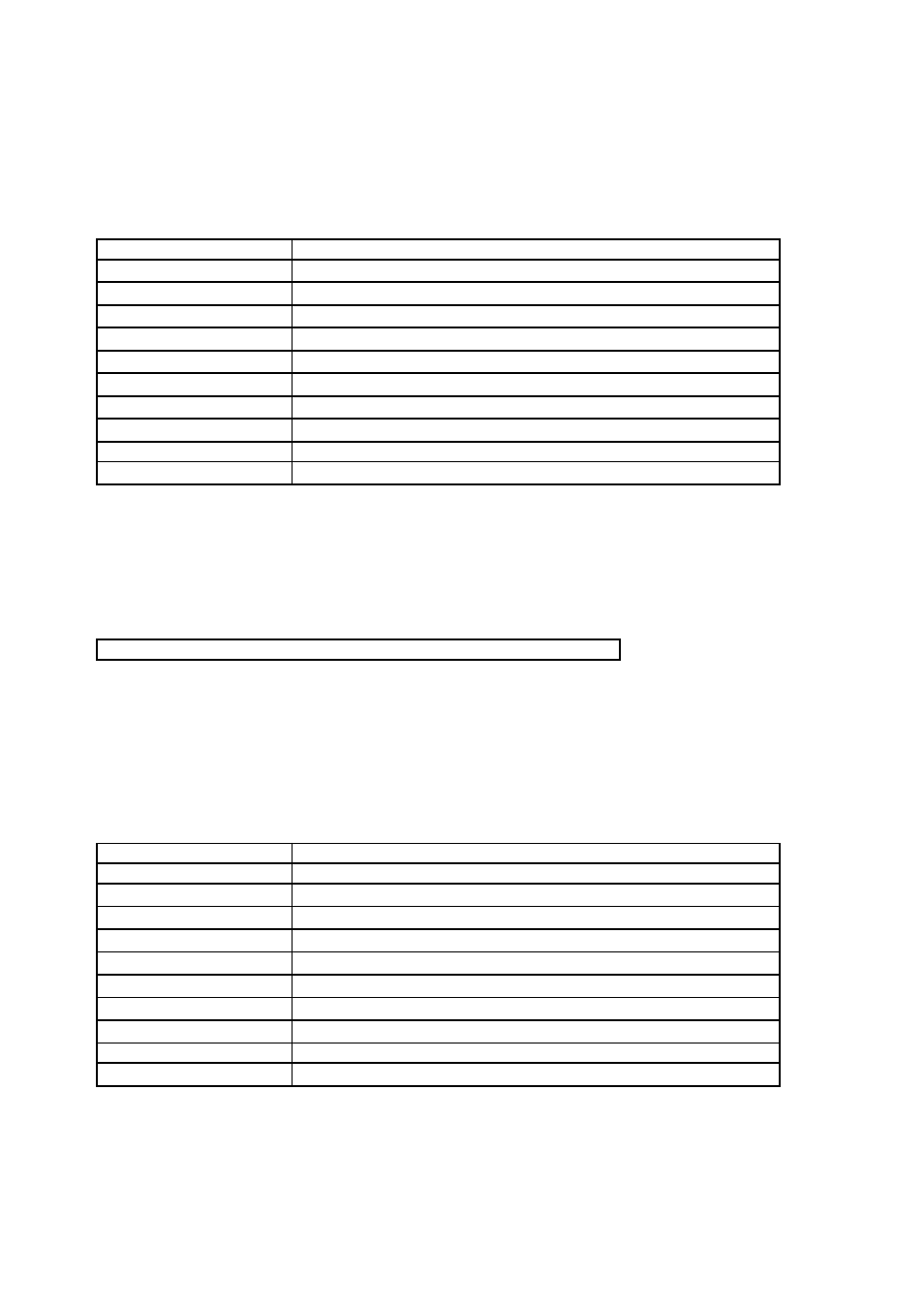

DVN5-DVN0

Φ

: Base clock divide-by-N (feedback to PLL)

000000

Base clock

(F

CL-MAIN

)

: 1 (no division)

000001

Base clock

(F

CL-MAIN

)

: 2 (division by 2)

000010

Base clock

(F

CL-MAIN

)

: 3 (division by 3)

000011

Base clock

(F

CL-MAIN

)

: 4 (division by 4)

000100

Base clock

(F

CL-MAIN

)

: 5 (division by 5)

000101

Base clock

(F

CL-MAIN

)

: 6 (division by 6)

000110

Base clock

(F

CL-MAIN

)

: 7 (division by 7)

000111

Base clock

(F

CL-MAIN

)

: 8 (division by 8)

......

.....

111111

Base clock

(F

CL-MAIN

)

: 64 (division by 64)

7

6

5

4

3

2

1

0

bit

-

-

-

-

DVG3

DVG2

DVG1

DVG0

0

0

0

0

0

0

0

0

Initial value (

INIT pin input,

watchdog reset

)

0

0

0

0

X

X

X

X

Initial value

(Software reset)

R0/W0

R0/W0

R0/W0

R0/W0

R/W

R/W

R/W

R/W

Attribute

DVG3-DVG0

PLL output divided-by-G start/end frequency (generates

Φ

: Base clock)

0000

Auto gear disabled (inital value)

0001

Source (F

CL-PLL

)

: 2 (division by 2)

0010

Source (F

CL-PLL

)

: 3 (division by 3)

0011

Source (F

CL-PLL

)

: 4 (division by 4)

0100

Source (F

CL-PLL

)

: 5 (division by 5)

0101

Source (F

CL-PLL

)

: 6 (division by 6)

0110

Source (F

CL-PLL

)

: 7 (division by 7)

0111

Source (F

CL-PLL

)

: 8 (division by 8)

......

.....

1111

Source (F

CL-PLL

)

: 16 (division by 16)