Chapter 20 software watchdog timer, Overview, Features – FUJITSU MB91460 SERIES FR60 User Manual

Page 289: Chapter 20, No.273), Chapters

273

Chapter 20 Software Watchdog Timer

1.Overview

Chapter 20 Software Watchdog Timer

1. Overview

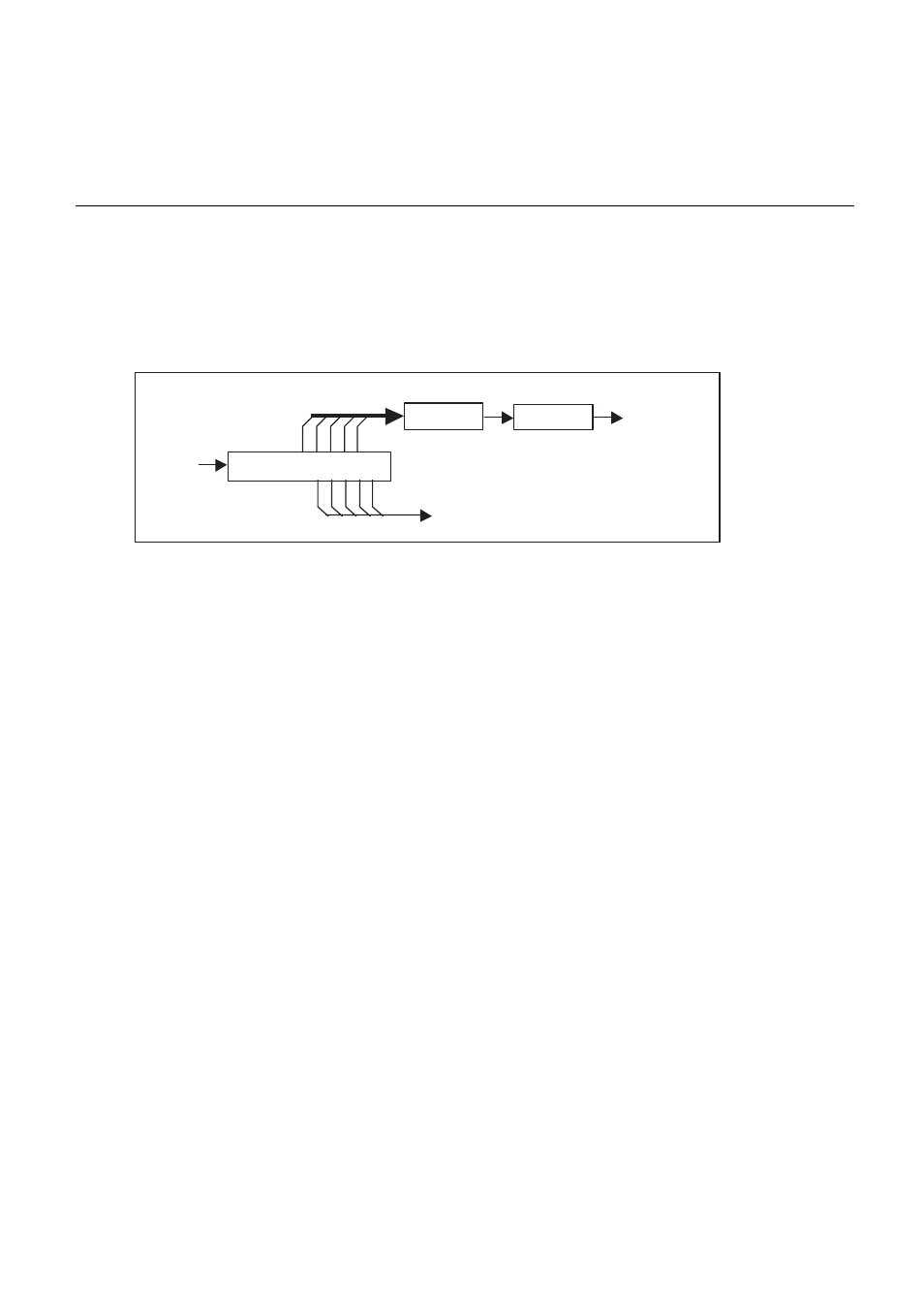

The software watchdog timer consists of a selector that uses the output from a 26-bit timebase counter using

the base clock (F) and a one-bit counter.

The watchdog timer generates the watchdog reset (initial setting reset) if the generation delay operation (an

interval watchdog reset) is disabled due to problems such as program runaway.

2. Features

■

Watchdog timer

• Type

: Generates the watchdog reset (INIT) with the overflow from one-bit counter

• Quantity

: 1

• Count clock (interval time): Bit output from the timebase timer

4 types

2

20

/F

F

, 2

22

/F

F

, 2

24

/F

F

, 2

26

/F

F

(Can be set only once after the reset (RST).)

• Clearing 1-bit counter:

Successively writes “A5”“5A” to watchdog reset generation delay register WPR by the software.

• Operation start/stop: This timer starts to operate once it writes data to the watchdog control register RSRR

for the first time after the reset (RST). This timer stops only by the reset (RST).

ƒEƒHƒbƒ`ƒhƒbƒO§Œä•”

ƒx[ƒX

ƒNƒ ƒbƒN

i ƒ³j

26 ƒrƒbƒgƒJƒEƒ“ƒ^

ƒZƒŒƒNƒ^

ƒJƒEƒ“ƒ^

ƒEƒHƒbƒ`ƒhƒbƒOƒ^ƒCƒ}

ƒ^ƒCƒƒx[ƒXƒ^ƒCƒ}

ƒEƒHƒbƒ`

ƒhƒbƒO

ƒŠƒZƒbƒg

ƒ^ƒCƒƒx[ƒX

ƒJƒEƒ“ƒ^

Watchdog control section

Base

clock

(f)

26-bit counter

Selector

Counter

Watchdog timer

Timebase timer

Watchdog

reset

Timebase

counter