Flash memory wait timing register (fmwt) – FUJITSU MB91460 SERIES FR60 User Manual

Page 191

175

Chapter 11 Memory Controller

8.Explanations of Registers

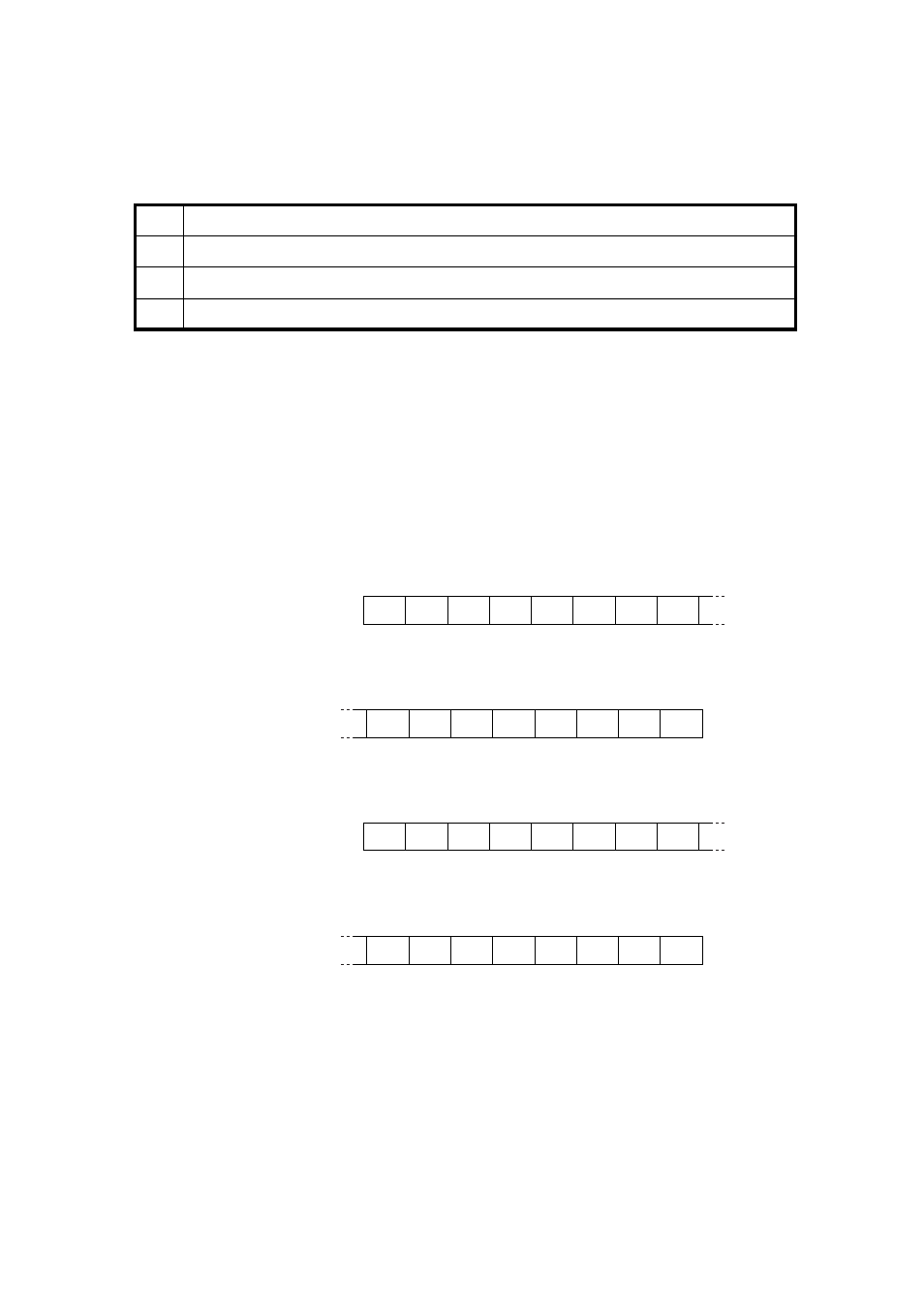

• BIT[1:0]: SZ[1:0] - Cache size configuration

The cache size is set to ’11’ after reset.

The cache size can be configured on the evaluation device (EVA).

Remark: The number of cache entries determines the TAG initialization period at device startup, see the explanai-

tion of the FLUSH bit above.

Important remark: On products with less than 16kByte instruction cache it is recommended to set the size configu-

ration in the system startup according to the available cache size.

Important remark: It is not allowed to set the cache size configuration (FCHCR.SZ[1:0]) and FLUSH at the same

time (same write access). Always first set the size configuration before flushing the cache.

●

FLASH Memory Wait Timing Register (FMWT)

Remarks:

• ATD[2:0] setting is 0x7 on MB91V460 and 0x5 on MB91F467DA

• EQ[3:0] setting is 0xF on MB91V460 and 0xD on MB91F467DA

• FMWT2 is not available on MB91V460

• BIT[31:30]: WTP[1:0] - Wait cycles for FLASH in page access

WTP is set to 3 after reset.

00

0kByte - Cache disabled

01

4kByte (1024 entries)

10

8kByte (2048 entries)

11

16kByte (4096 entries) (default)

WTP1

WTP0 WEXH1 WEXH0 WTC3 WTC2

WTC1

WTC0

⇐

Bit no.

Read/write

⇒

(R/W) (R/W) (R/W) (R/W) (R/W) (R/W) (R/W) (R/W)

Default value

⇒

(1)

(1)

(1)

(1)

(1)

(1)

(1)

(1)

Wait Timing Register byte 0

Address : 7004

H

31

30

29

28

27

26

25

24

FMWT

(FRAM) ATD2

ATD1

ATD0

EQ3

EQ2

EQ1

EQ0

⇐

Bit no.

Read/write

⇒

(R/W) (R/W) (R/W) (R/W) (R/W) (R/W) (R/W) (R/W)

Default value

⇒

(0)

(1)

(1/0)

(1)

(1)

(1)

(1/0)

(1)

Address : 7005

H

23

22

21

20

19

18

17

16

FMWT

Wait Timing Register byte 1

-

ALEH2 ALEH1 ALEH0

-

-

-

-

⇐

Bit no.

Read/write

⇒

(-)

(1)

(0)

(1)

(-)

(-)

(-)

(-)

Default value

⇒

(X)

(R/W) (R/W) (R/W)

(X)

(X)

(X)

(X)

Wait Timing Register byte 2

Address : 7006

H

15

14

13

12

11

10

9

8

FMWT2

-

-

-

-

-

PS2

PS1

PS0

⇐

Bit no.

Read/write

⇒

(-)

(-)

(-)

(-)

(-)

(R/W) (R/W) (R/W)

Default value

⇒

(X)

(X)

(X)

(X)

(X)

(0)

(0)

(0)

Address : 7007

H

7

6

5

4

3

2

1

0

FMPS

Wait Timing Register byte 3