2 hardware reset description – FUJITSU MB91460 SERIES FR60 User Manual

Page 711

695

Chapter 34 CAN Controller

2.Register Description

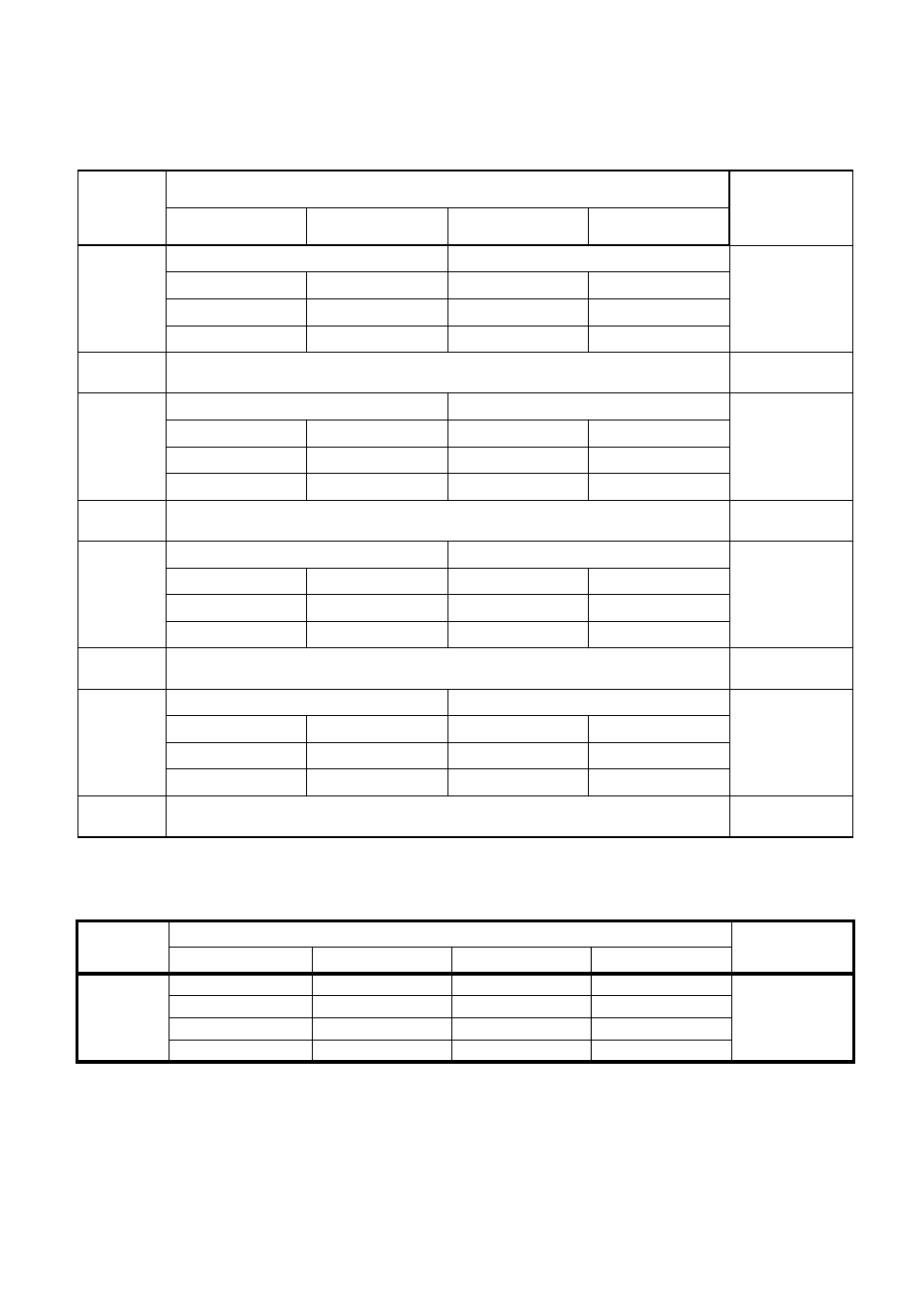

Figure 2-1 CAN Register Summary

Figure 2-2 CAN Prescaler Register Summary

2.2 Hardware Reset Description

After hardware reset, the registers of the CAN hold the values described in

.

Base-addr +

0x80

Transmission Request Register 2

Transmission Request Register 1

Transmission

Request Register is

read only.

bit[15:8]

bit[7:0]

bit[15:8]

bit[7:0]

TxRqst[32-25]

TxRqst[24-17]

TxRqst[16-9]

TxRqst[8-1]

Reset: 0x00

Reset: 0x00

Reset: 0x00

Reset: 0x00

Base-addr +

0x84

Reserved ( >32..128 Message buffer)

Base-addr +

0x90

New Data 2

New Data 1

New Data is read

only.

bit[15:8]

bit[7:0]

bit[15:8]

bit[7:0]

NewDat[32-25]

NewDat[24-17]

NewDat[16-9]

NewDat[8-1]

Reset: 0x00

Reset: 0x00

Reset: 0x00

Reset: 0x00

Base-addr +

0x94

Reserved ( >32..128 Message buffer)

Base-addr +

0xA0

Interrupt Pending 2

Interrupt Pending 1

Interrupt Pending is

read only.

bit[15:8]

bit[7:0]

bit[15:8]

bit[7:0]

IntPnd[32-25]

IntPnd[24-17]

IntPnd[16-9]

IntPnd[8-1]

Reset: 0x00

Reset: 0x00

Reset: 0x00

Reset: 0x00

Base-addr +

0xA4

Reserved ( >32..128 Message buffer)

Base-addr +

0xB0

Message Valid 2

Message Valid 1

Message Valid is

read only.

bit[15:8]

bit[7:0]

bit[15:8]

bit[7:0]

MsgVal[32-25]

MsgVal[24-17]

MsgVal[16-9]

MsgVal[8-1]

Reset: 0x00

Reset: 0x00

Reset: 0x00

Reset: 0x00

Base-addr +

0xB4

Reserved ( >32..128 Message buffer)

Address

Register

Note

+0

+1

+2

+3

0x04C0

CANPRE

CANCKD

-

-

CAN Prescaler

bit[3:0]

bit[5:0]

-

-

CANPRE[3:0]

CANCKD[5:0]

-

-

Reset: 0x00

Reset: 0x00

-

-

Address

Register

Note

+0

+1

+2

+3