Dram control register (dcr) bit definitions -25 – Motorola DSP56301 User Manual

Page 99

Bus Interface Unit (BIU) Registers

Core Configuration

4

-25

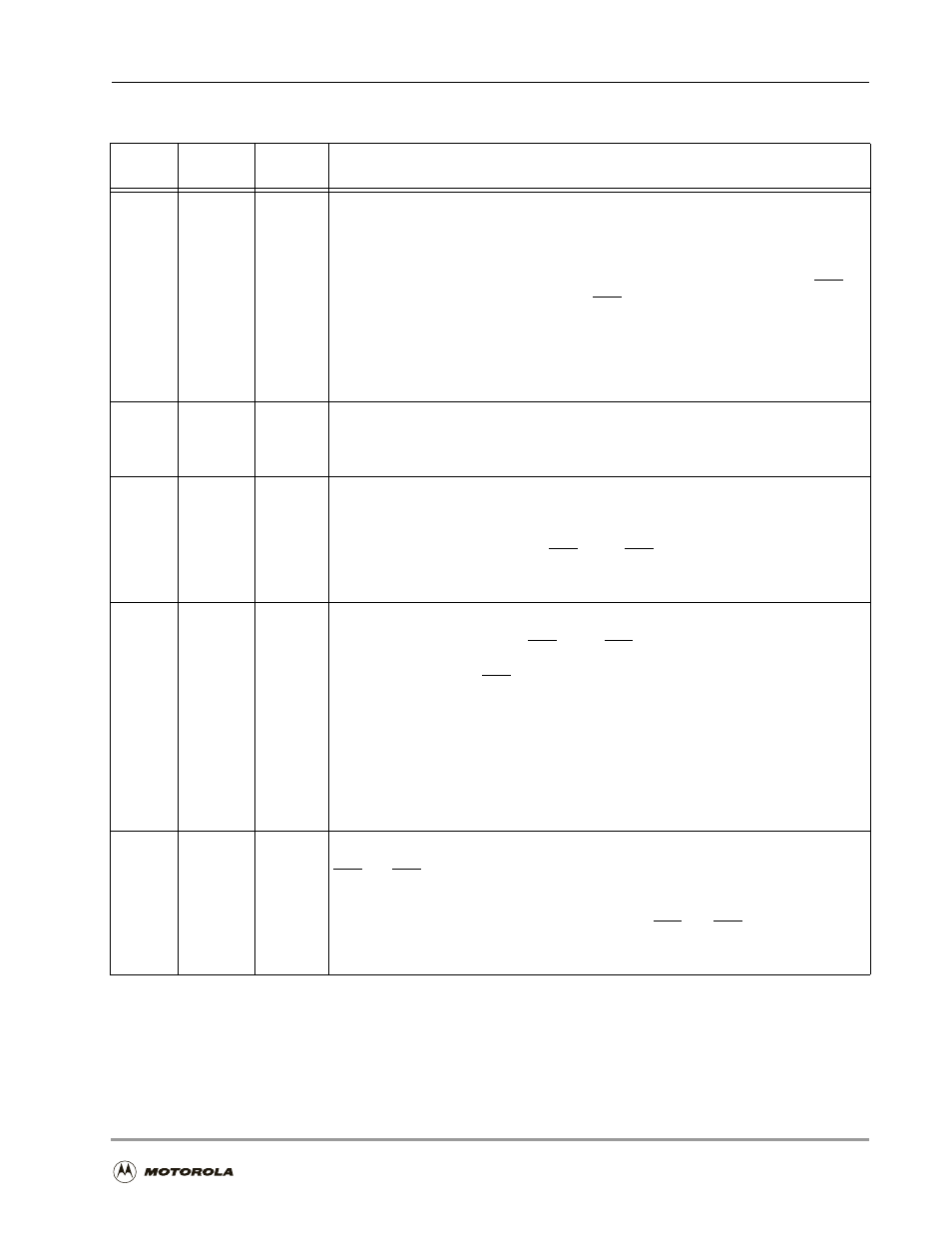

Table 4-10. DRAM Control Register (DCR) Bit Definitions

Bit

Number

Bit Name

Reset

Value

Description

23 BRP

0

Bus Refresh Prescaler

Controls a prescaler in series with the refresh clock divider. If BPR is set, a

divide-by-64 prescaler is connected in series with the refresh clock divider. If BPR is

cleared, the prescaler is bypassed. The refresh request rate (in clock cycles) is the

value written to BRF[7–0] bits + 1, multiplied by 64 (if BRP is set) or by one (if BRP is

cleared). When programming the periodic refresh rate, you must consider the RAS

time-out period. Hardware support for the RAS time-out restriction does not exist

.

Note:

Refresh requests are not accumulated and, therefore, in a fast refresh request

rate not all the refresh requests are served (for example, the combination

BRF[7–0] = $00 and BRP = 0 generates a refresh request every clock cycle,

but a refresh access takes at least five clock cycles).

22–15

BRF[7–0]

0

Bus Refresh Rate

Controls the refresh request rate. The BRF[7–0] bits specify a divide rate of 1–256

(BRF[7–0] = $00–$FF). A refresh request is generated each time the refresh counter

reaches zero if the refresh counter is enabled (BRE = 1).

14

BSTR

0

Bus Software Triggered Reset

Generates a software-triggered refresh request. When BSTR is set, a refresh request

is generated and a refresh access is executed to all DRAM banks (the exact timing of

the refresh access depends on the pending external accesses and the status of the

BME bit). After the refresh access (CAS before RAS) is executed, the DRAM controller

hardware clears the BSTR bit. The refresh cycle length depends on the BRW[1–0] bits

(a refresh access is as long as the out-of-page access).

13

BREN

0

Bus Refresh Enable

Enables/disables the internal refresh counter. When BREN is set, the refresh counter is

enabled and a refresh request (CAS before RAS) is generated each time the refresh

counter reaches zero. A refresh cycle occurs for all DRAM banks together (that is, all

pins that are defined as RAS are asserted together). When this bit is cleared, the

refresh counter is disabled and a refresh request may be software triggered by using

the BSTR bit. In a system in which DSPs share the same DRAM, the DRAM controller

of more than one DSP may be active, but it is recommended that only one DSP have

its BREN bit set and that bus mastership is requested for a refresh access. If BREN is

set and a WAIT instruction is executed, periodic refresh is still generated each time the

refresh counter reaches zero. If BREN is set and a STOP instruction is executed,

periodic refresh is not generated and the refresh counter is disabled. The contents of

the DRAM are lost.

12

BME

0

Bus Mastership Enable

Enables/disables interface to a local DRAM for the DSP. When BME is cleared, the

RAS and CAS pins are tri-stated when mastership is lost. Therefore, you must connect

an external pull-up resistor to these pins. In this case (BME = 0), the DSP DRAM

controller assumes a page fault each time the mastership is lost. A DRAM refresh

requires a bus mastership. If the BME bit is set, the RAS and CAS pins are always

driven from the DSP. Therefore, DRAM refresh can be performed, even if the DSP is

not the bus master.