Motorola DSP56301 User Manual

Page 182

Host-Side Programming Model

6

-64

DSP56301 User’s Manual

6.8.7

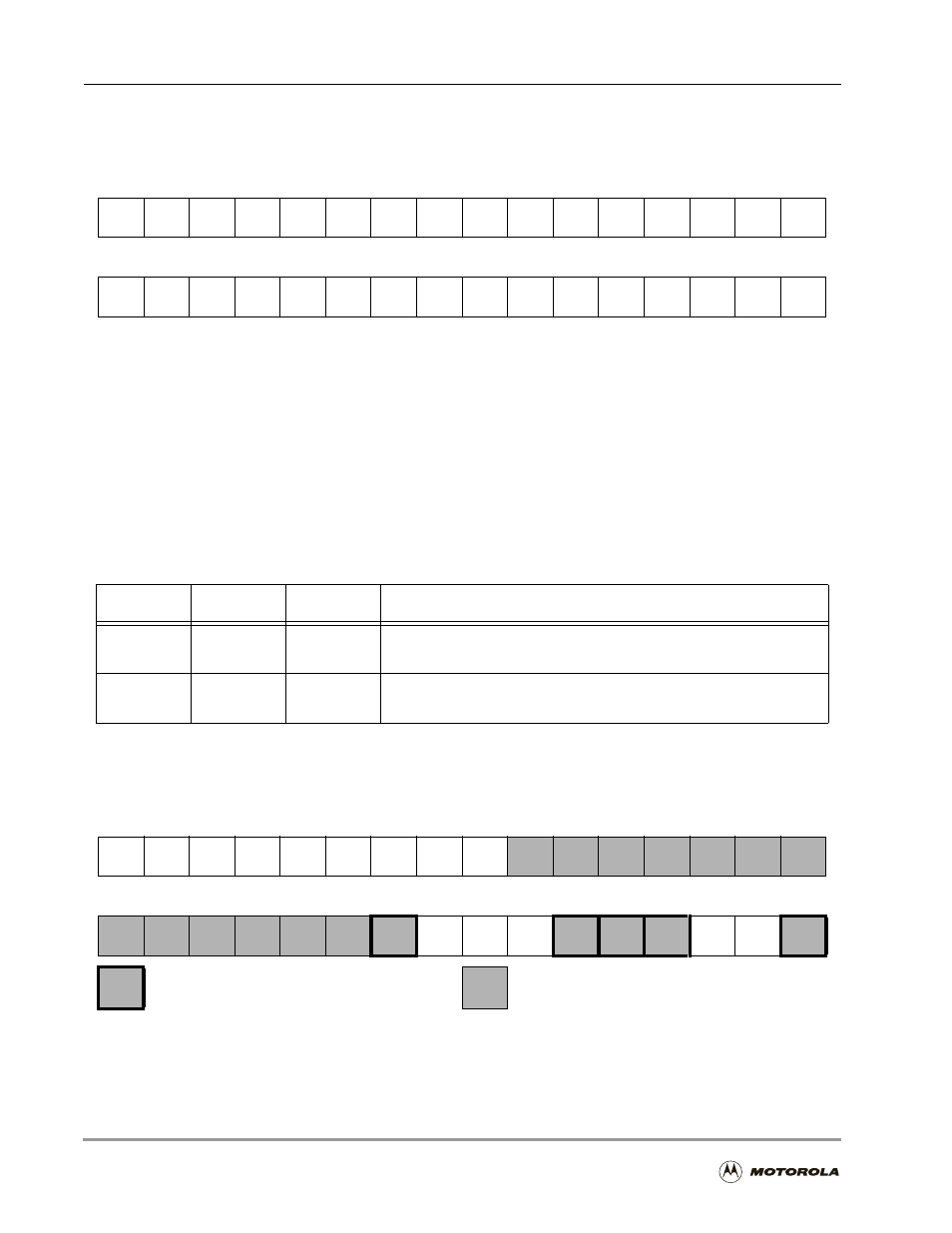

Device ID/Vendor ID Configuration Register (CDID/CVID)

r

A PCI-standard 32-bit read-only register mapped into the PCI configuration space in PCI

mode or in mode 0 (DCTR[HM]

=

$1 or $0). CDID/CVID is accessed if a configuration read

command is in progress and the PCI address is $00. The DID[15–0] bits identify the DSP.

The VID[15–0] bits identify the manufacturer of the DSP. The contents of CDID/CVID are

hardwired and are unaffected by any type of reset. The host processor can access CDID/CVID

only when the HI32 is in PCI mode (DCTR[HM]

≠

$1).

6.8.8

Status/Command Configuration Register (CSTR/CCMR)

r

A PCI-standard 32-bit read/write register mapped into the PCI configuration space in PCI

mode or in mode 0 (DCTR[HM]

=

$1 or $0). CSTR/CCMR is accessed if a configuration

31

30

29

28

27

26

25

24

23

22

21

20

19

18

17

16

DID15 DID14 DID13 DID12 DID11 DID10 DID9

DID8

DID7

DID6

DID5

DID4

DID3

DID2

DID1

DID0

15

14

13

12

11

10

9

8

7

6

5

4

3

2

1

0

VID15 VID14 VID13 VID12 VID11 VID10 VID9

VID8

VID7

VID6

VID5

VID4

VID3

VID2

VID1

VID0

Figure 6-16. Device/Vendor ID Configuration Register (CDID/CVID)

Table 6-25. Device ID/Vendor ID Configuration Register (CDID/CVID) Bit Definitions

Bit Number

Bit Name

Reset Value

Description

31–16

DID[15–0]

Hardwired

Device ID

$1801 = DSP56301

15–0

VIV[15–0]

Hardwired

Vendor ID

$1057

31

30

29

28

27

26

25

24

23

22

21

20

19

18

17

16

DPE

SSE

RMA

RTA

STA

DST1 DST0

DPR FBBC

15

14

13

12

11

10

9

8

7

6

5

4

3

2

1

0

SERE WCC PERR

BM

MSE

Not implemented, read as zero, should be

written as zero

Reserved, read as zero and should be written

as zero

Figure 6-17. Status/Command Configuration Register (CSTR/CCMR)