Motorola DSP56301 User Manual

Page 293

Triple Timer Module Programming Model

Triple Timer Module

9

-31

7–4

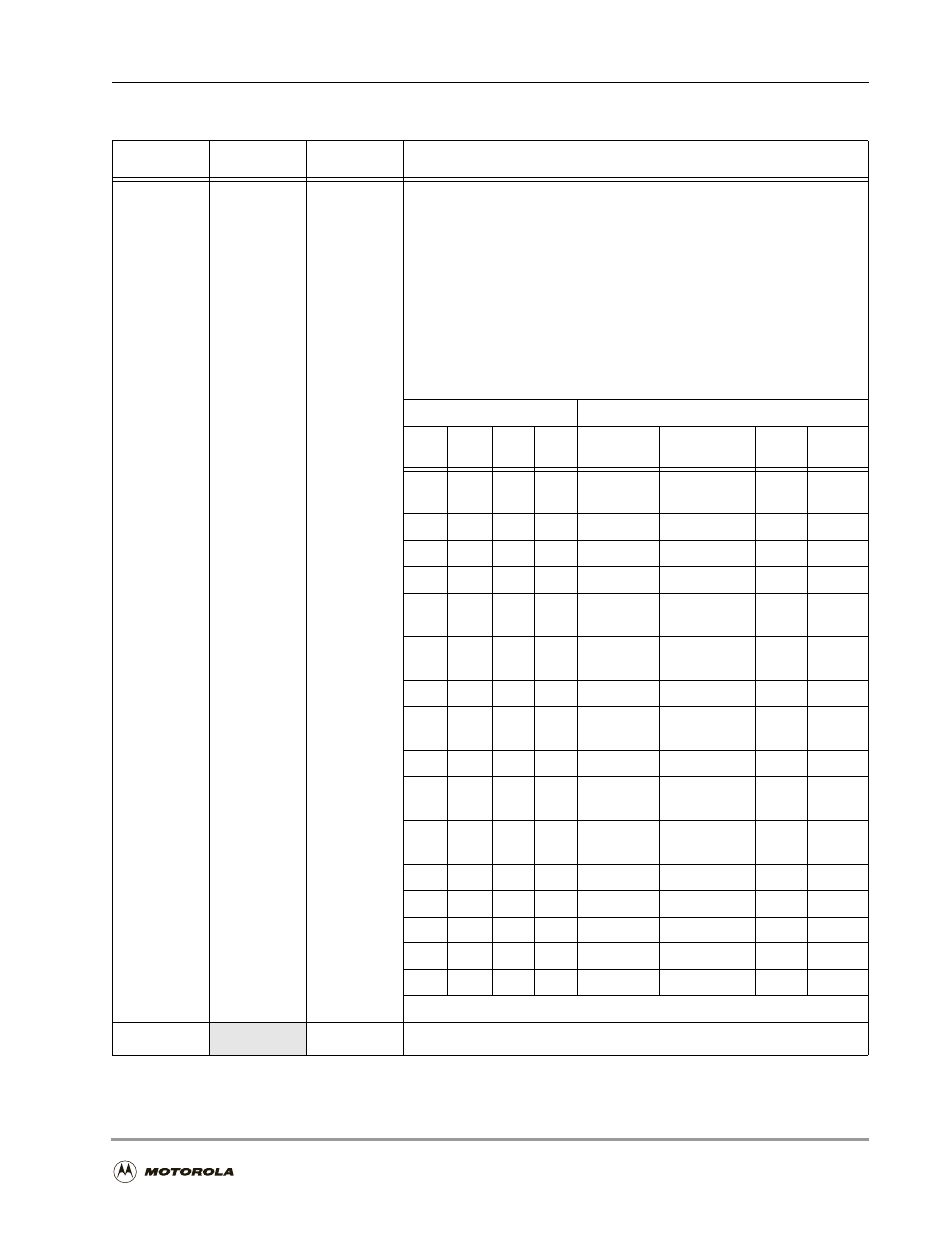

TC[3–0]

0

Timer Control

Control the source of the timer clock, the behavior of the TIO signal, and

the Timer mode of operation. Section 9.3,

describes the timer operating modes in detail.

NOTE: To ensure proper operation, the TC[3–0] bits should be changed

only when the timer is disabled (that is, when the TCSR[TE] bit is cleared)

NOTE: If the clock is external, the counter is incremented by the transitions

on the TIO signal. The external clock is internally synchronized to the

internal clock, and its frequency should be lower than the internal

operating frequency divided by 4 (that is, CLK/4).

Bit Settings

Mode Characteristics

TC3

TC2

TC1

TC0

Mode

Number

Mode

Function

TIO

Clock

0

0

0

0

0

Timer and

GPIO

GPIO

1

Internal

0

0

0

1

1

Timer pulse

Output Internal

0

0

1

0

2

Timer toggle

Output Internal

0

0

1

1

3

Event counter

Input

External

0

1

0

0

4

Input width

measurement

Input

Internal

0

1

0

1

5

Input period

measurement

Input

Internal

0

1

1

0

6

Capture event

Input

Internal

0

1

1

1

7

Pulse width

modulation

Output Internal

1

0

0

0

8

Reserved

—

—

1

0

0

1

9

Watchdog

pulse

Output Internal

1

0

1

0

10

Watchdog

Toggle

Output Internal

1

0

1

1

11

Reserved

—

—

1

1

0

0

12

Reserved

—

—

1

1

0

1

13

Reserved

—

—

1

1

1

0

14

Reserved

—

—

1

1

1

1

15

Reserved

—

—

Note 1: The GPIO function is enabled only if all of the TC[3–0] bits are 0.

3

0

Reserved. Write to zero for future compatibility.

Table 9-3. Timer Control/Status Register (TCSR) Bit Definitions (Continued)

Bit Number

Bit Name

Reset Value

Description