8 host-side programming model, Host-side programming model -44, Hi32 programming model, host-side registers -44 – Motorola DSP56301 User Manual

Page 162: 8 host-side programming model

Host-Side Programming Model

6

-44

DSP56301 User’s Manual

6.8

Host-Side Programming Model

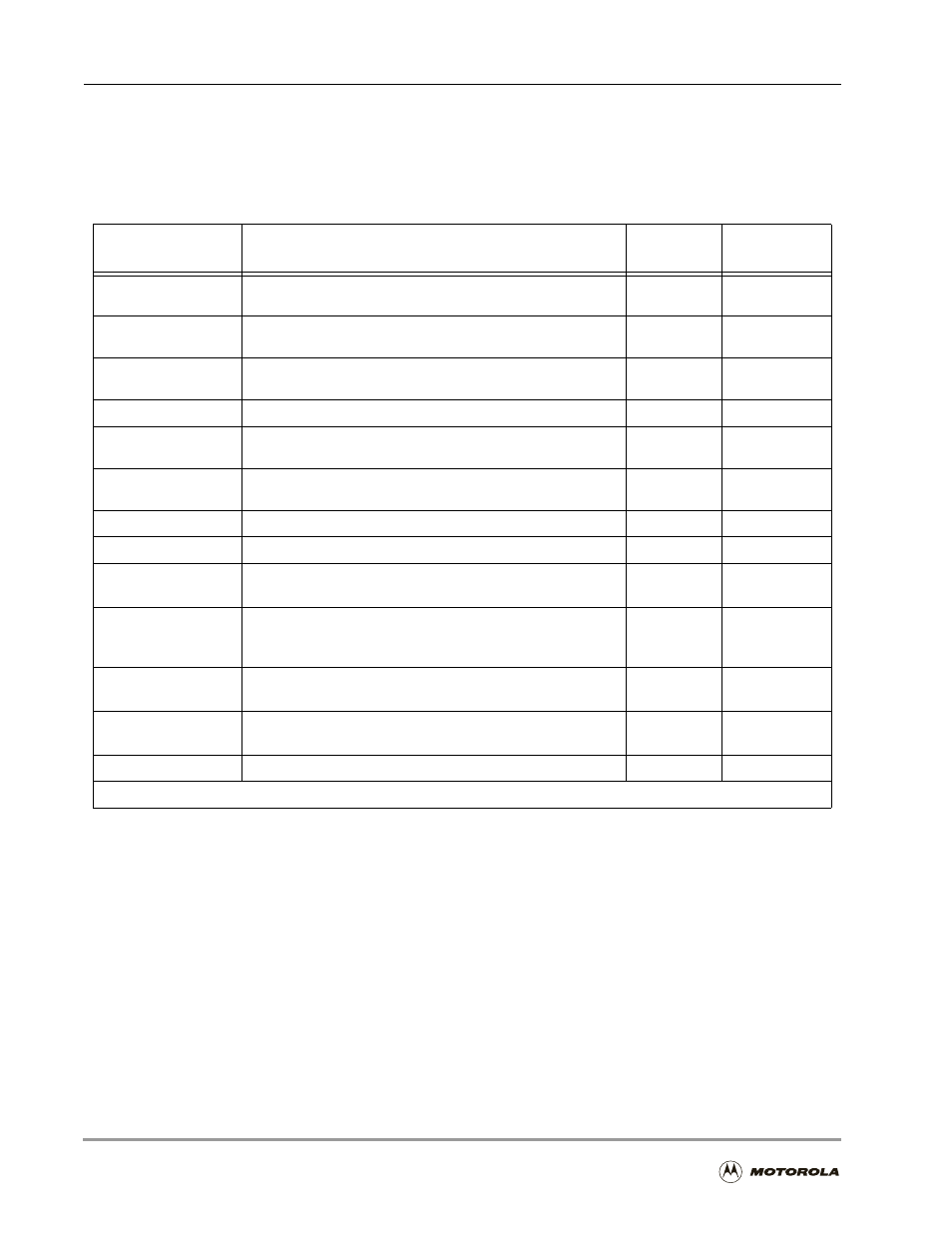

The HI32 appears to the host processor as a bank of registers, listed in Table 6-17.

In the Universal Bus modes:

n

The HI32 occupies eight words in the host processor address space. The host processor

cannot access the PCI configuration registers (CDID/CVID, CSTR/CCMR,

CCCR/CRID, CHTY/CLAT, CBMA, CSID, and CILP) in the Universal Bus modes.

However, it can configure these registers in Self-Configuration mode.

n

Because of the fast DSP56300 core interrupt response, most host microprocessors can

read or write data at their maximum programmed non-DMA instruction rate without

testing the handshake flags for each transfer. If the full interrupt driven handshake is

not needed, the high-speed data transfer between the host and the HI32 can be

supported with only the host data strobe/acknowledge handshake mechanism. DMA

Table 6-17. HI32 Programming Model, Host-Side Registers

X Memory Register

Address

Register

Mode

Page

Host Interface Control Register (HCTR)

UBM

PCI

Host Interface Status Register (HSTR)

UBM

PCI

Host Command Vector Register (HCVR)

UBM

PCI

Host Master Receive Data Register (HRXM)

PCI

Host Slave Receive Data Register (HRXS)

UBM

PCI

Host Transmit Data Register (HTXR)

UBM

PCI

Device ID/Vendor ID Configuration Register (CDID/CVID)

PCI

Status/Command Configuration Register (CSTR/CCMR)

PCI

Class Code/Revision ID Configuration Register

(CCCR/CRID)

PCI

Header Type/Latency Timer Configuration Register

Cache Line Size Configuration Register

(CHTY/CLAT/CCLS)

UBM

PCI

Memory Space Base Address Configuration Register

(CBMA)

UBM

PCI

Subsystem ID and Subsystem Vendor ID Configuration

Register

(CSID)

PCI

Interrupt Line-Interrupt Signal Configuration Register (CILP)

PCI

Note:

As the PCI master, the HI32 uses the HRXM to output data, and the host bus cannot access this register.