Motorola DSP56301 User Manual

Page 147

HI32 DSP-Side Programming Model

Host Interface (HI32)

6

-29

14

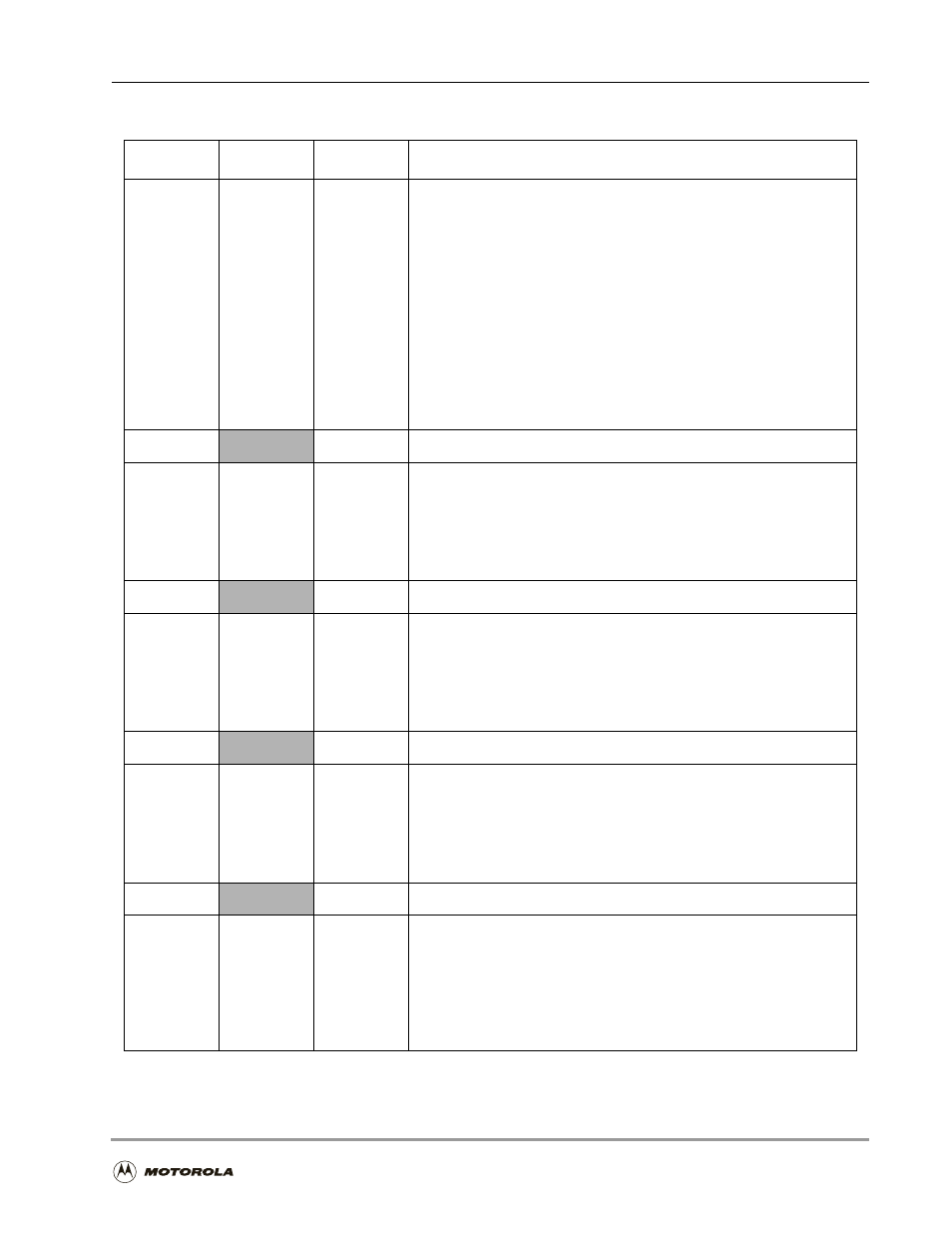

CLRT

0

Clear Transmitter

Clears the HI32 master-to-host bus data path in PCI mode (DCTR[HM]

= $1). When the DSP56300 core sets CLRT, the HI32 hardware clears

the master DSP-to-host bus data path (that is, the DTXM-HRXM FIFO

is forced empty), thus setting the PCI Master Transmit Data Request bit

(MTRQ) in the DPSR. Then it clears CLRT. The DSP56300 core cannot

write a value of zero to CLRT. To assure operation, the DSP56300 core

can set CLRT only under the following conditions:

1.

MARQ is set in the DPSR (that is, the DSP56300 core has not

initiated a PCI transaction).

2.

No DSP56300 core DMA channel is enabled to service HI32

master transmit data DMA requests.

CLRT is ignored when the HI32 is not in PCI mode (DCTR[HM]

≠

$1).

13

0

Reserved. Write to 0 for future compatibility.

12 TCIE

0

Transfer Complete Interrupt Enable

Enables/disables a DSP56300 core interrupt request in PCI mode

(DCTR[HM] = $1). The request is generated if the host data transfer

complete (HDTC) status bit in the DSP PCI Status Register (DPSR) is

set. When TCIE is cleared, transfer complete interrupt requests are

disabled.

11–10

0

Reserved. Write to 0 for future compatibility.

9

TTIE

0

Transaction Termination Interrupt Enable

Enables/disables a DSP56300 core interrupt request in PCI mode

(DCTR[HM]

=

$1) when the HI32, as a PCI master, executes a time-out

termination (TO is set), a target-initiated disconnect (DPSR[TDIS] is

set), or a retry termination (TRTY is set). When TTIE is cleared,

transaction termination interrupt requests are disabled.

8

0

Reserved. Write to 0 for future compatibility.

7

TAIE

0

Transaction Abort Interrupt Enable

Enables/disables a DSP56300 core interrupt request in PCI mode

(DCTR[HM]

=

$1) when the HI32, as a PCI master, executes a

master-abort termination (DPSR[MAB] is set) or a target initiated

target-abort termination (TAB is set). If TAIE is cleared, transaction

abort interrupt requests are disabled.

6

0

Reserved. Write to 0 for future compatibility.

5

PEIE

0

Parity Error Interrupt Enable

Enables/disables a DSP56300 core interrupt request when a parity

error is detected in PCI mode (DCTR[HM]

=

$1). When PEIE is cleared,

parity error interrupt requests are disabled. When PEIE is set, a parity

error interrupt request is generated if a parity error (address or data) is

detected and the address parity error (APER) status bit or the data

parity error (DPER) status bit in the DPSR is set.

Table 6-11. DSP PCI Control Register (DPCR) Bit Definitions (Continued)

Bit Number

Bit Name

Reset Value

Description