Motorola DSP56301 User Manual

Page 251

SCI Programming Model

Serial Communication Interface (SCI)

8

-15

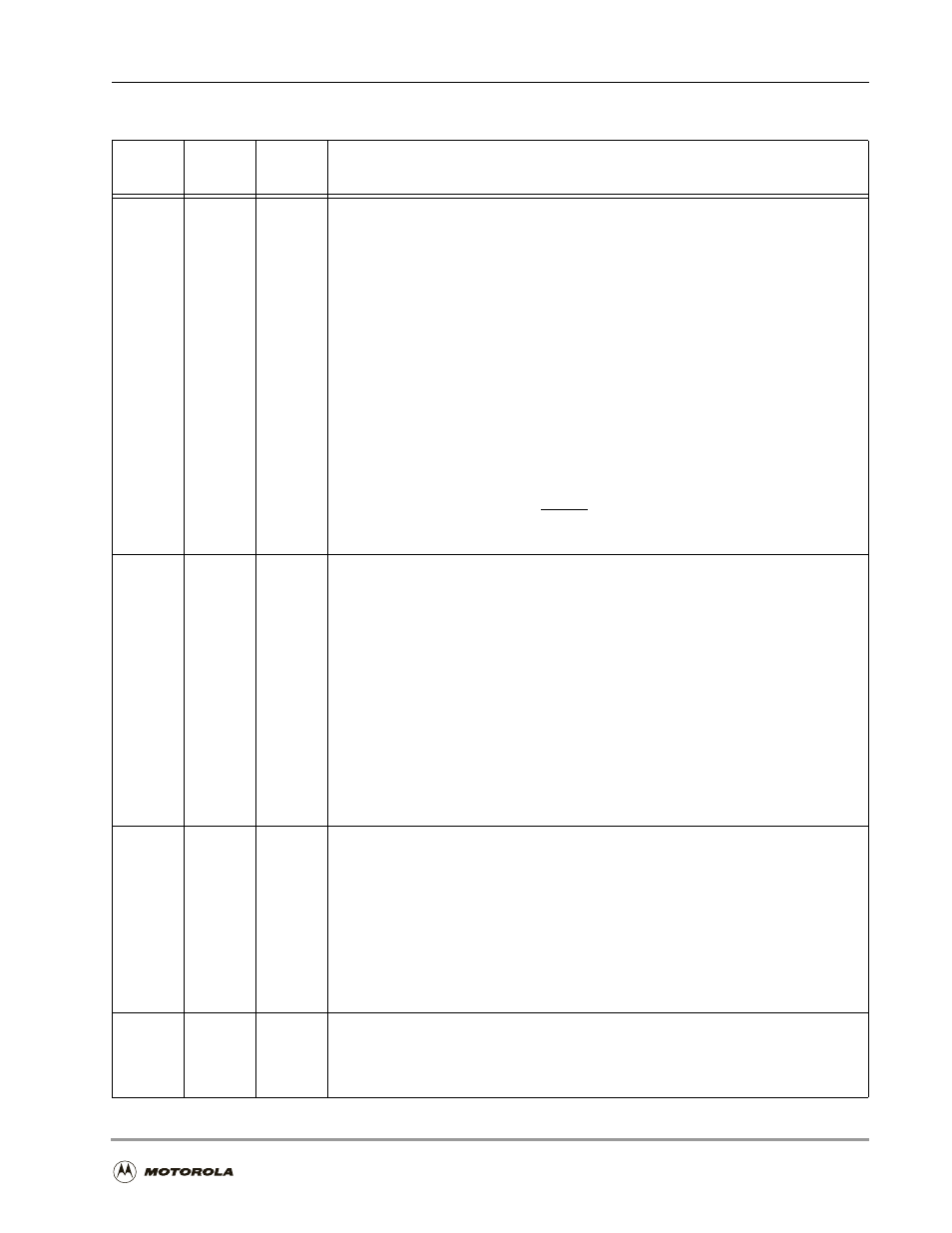

6

RWU

0

Receiver Wakeup Enable

When RWU is set and the SCI is in Asynchronous mode, the wakeup function is

enabled; i. e., the SCI is asleep and can be awakened by the event defined by the

WAKE bit. In Sleep state, all interrupts and all receive flags except IDLE are disabled.

When the receiver wakes up, RWU is cleared by the wakeup hardware. You can also

clear the RWU bit to wake up the receiver. You can use RWU to ignore messages that

are for other devices on a multidrop serial network. Wakeup on idle line (i. e., WAKE is

cleared) or wakeup on address bit (i. e., WAKE is set) must be chosen. When WAKE is

cleared and RWU is set, the receiver does not respond to data on the data line until an

idle line is detected. When WAKE is set and RWU is set, the receiver does not respond

to data on the data line until a data frame with Bit 9 set is detected.

When the receiver wakes up, the RWU bit is cleared, and the first frame of data is

received. If interrupts are enabled, the CPU is interrupted and the interrupt routine

reads the message header to determine whether the message is intended for this DSP.

If the message is for this DSP, the message is received, and RWU is set to wait for the

next message. If the message is not for this DSP, the DSP immediately sets RWU.

Setting RWU causes the DSP to ignore the remainder of the message and wait for the

next message. Either a hardware RESET signal or a software RESET instruction

clears RWU. RWU is ignored in Synchronous mode.

5

WAKE

0

Wakeup Mode Select

When WAKE is cleared, the wakeup on Idle Line mode is selected. In the wakeup on

idle line mode, the SCI receiver is re-enabled by an idle string of at least 10 or 11

(depending on WDS mode) consecutive ones. The transmitter’s software must provide

this idle string between consecutive messages. The idle string cannot occur within a

valid message because each word frame there contains a start bit that is 0.

When WAKE is set, the wakeup on address bit mode is selected. In the wakeup on

address bit mode, the SCI receiver is re-enabled when the last (eighth or ninth) data bit

received in a character (frame) is 1. The ninth data bit is the address bit (R8) in the

11-bit multidrop mode; the eighth data bit is the address bit in the 10-bit asynchronous

and 11-bit asynchronous with parity modes. Thus, the received character is an address

that has to be processed by all sleeping processors—that is, each processor has to

compare the received character with its own address and decide whether to receive or

ignore all following characters.

4

SBK

0

Send Break

A break is an all-zero word frame—a start bit 0, characters of all zeros (including any

parity), and a stop bit 0 (that is, ten or eleven zeros, depending on the mode selected).

If SBK is set and then cleared, the transmitter finishes transmitting the current frame,

sends 10 or 11 0s, and reverts to idle or sending data. If SBK remains set, the

transmitter continually sends whole frames of 0s (10 or 11 bits with no stop bit). At the

end of the break code, the transmitter sends at least one high (set) bit before

transmitting any data to guarantee recognition of a valid start bit. Break can signal an

unusual condition, message, and so on, by forcing a frame error; the frame error is

caused by a missing stop bit.

3

SSFTD

0

SCI Shift Direction

Determines the order in which the SCI data shift registers shift data in or out: MSB first

when set, LSB first when cleared. The parity and data type bits do not change their

position in the frame, and they remain adjacent to the stop bit.

Table 8-2. SCI Control Register (SCR) Bit Definitions (Continued)

Bit

Number

Bit Name

Reset

Value

Description