Motorola DSP56301 User Manual

Page 214

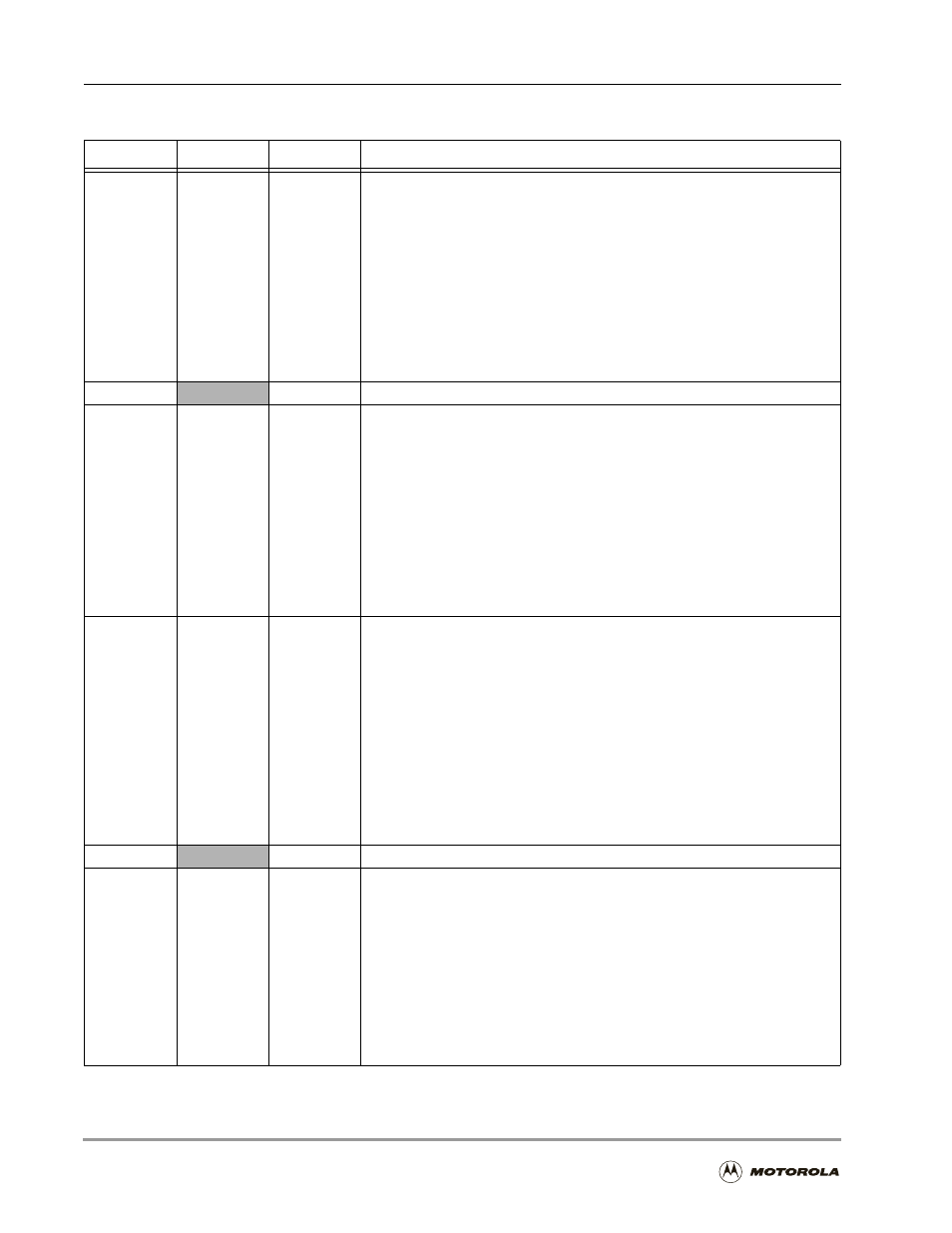

ESSI Programming Model

7

-16

DSP56301 User’s Manual

18

ALC

0

Alignment Control

The ESSI handles 24-bit fractional data. Shorter data words are left-aligned

to the MSB, bit 23. For applications that use 16-bit fractional data, shorter

data words are left-aligned to bit 15. The ALC bit supports shorter data

words. If ALC is set, received words are left-aligned to bit 15 in the receive

shift register. Transmitted words must be left-aligned to bit 15 in the transmit

shift register. If the ALC bit is cleared, received words are left-aligned to bit

23 in the receive shift register. Transmitted words must be left-aligned to bit

23 in the transmit shift register.

Note:

If the ALC bit is set, only 8-, 12-, or 16-bit words are used. The use

of 24- or 32-bit words leads to unpredictable results.

17

Reserved. Write to 0 for future compatibility.

16–12

DC[4–0]

0

Frame Rate Divider Control

Control the divide ratio for the programmable frame rate dividers that

generate the frame clocks. In Network mode, this ratio is the number of

words per frame minus one. In Normal mode, this ratio determines the word

transfer rate. The divide ratio ranges from 1 to 32 (DC = 00000 to 11111) for

Normal mode and 2 to 32 (DC = 00001 to 11111) for Network mode. A divide

ratio of one (DC = 00000) in Network mode is a special case known as

On-Demand mode. In Normal mode, a divide ratio of one (DC = 00000)

provides continuous periodic data word transfers. A bit-length frame sync

must be used in this case; you select it by setting the FSL[1–0] bits in the

CRA to (01). Figure 7-4 shows the ESSI frame sync generator functional

block diagram.

11

PSR

0

Prescaler Range

Controls a fixed divide-by-eight prescaler in series with the variable

prescaler. This bit extends the range of the prescaler when a slower bit clock

is needed. When PSR is set, the fixed prescaler is bypassed. When PSR is

cleared, the fixed divide-by-eight prescaler is operational, as in Figure 7-3.

This definition is reversed from that of the SSI in other DSP56000 family

members. The maximum allowed internally generated bit clock frequency is

the internal DSP56301 clock frequency divided by 4; the minimum possible

internally generated bit clock frequency is the DSP56301 internal clock

frequency divided by 4096.

Note:

The combination PSR = 1 and PM[7–0] = $00 (dividing F

core

by 2)

can cause synchronization problems and thus should not be used.

10–8

0

Reserved. Write to 0 for future compatibility.

7–0

PM[7–0]

0

Prescale Modulus Select

Specify the divide ratio of the prescale divider in the ESSI clock generator. A

divide ratio from 1 to 256 (PM = $0 to $FF) can be selected. The bit clock

output is available at the transmit clock signal (SCK) and/or the receive clock

(SC0) signal of the DSP. The bit clock output is also available internally for

use as the bit clock to shift the transmit and receive shift registers. Figure 7-3

shows the ESSI clock generator functional block diagram. F

core

is the

DSP56301 core clock frequency (the same frequency as the enabled

CLKOUT signal). Careful choice of the crystal oscillator frequency and the

prescaler modulus can generate the industry-standard CODEC master clock

frequencies of 2.048 MHz, 1.544 MHz, and 1.536 MHz.

Table 7-3. ESSI Control Register A (CRA) Bit Definitions (Continued)

Bit Number

Bit Name

Reset Value

Description