Motorola DSP56301 User Manual

Page 157

HI32 DSP-Side Programming Model

Host Interface (HI32)

6

-39

14

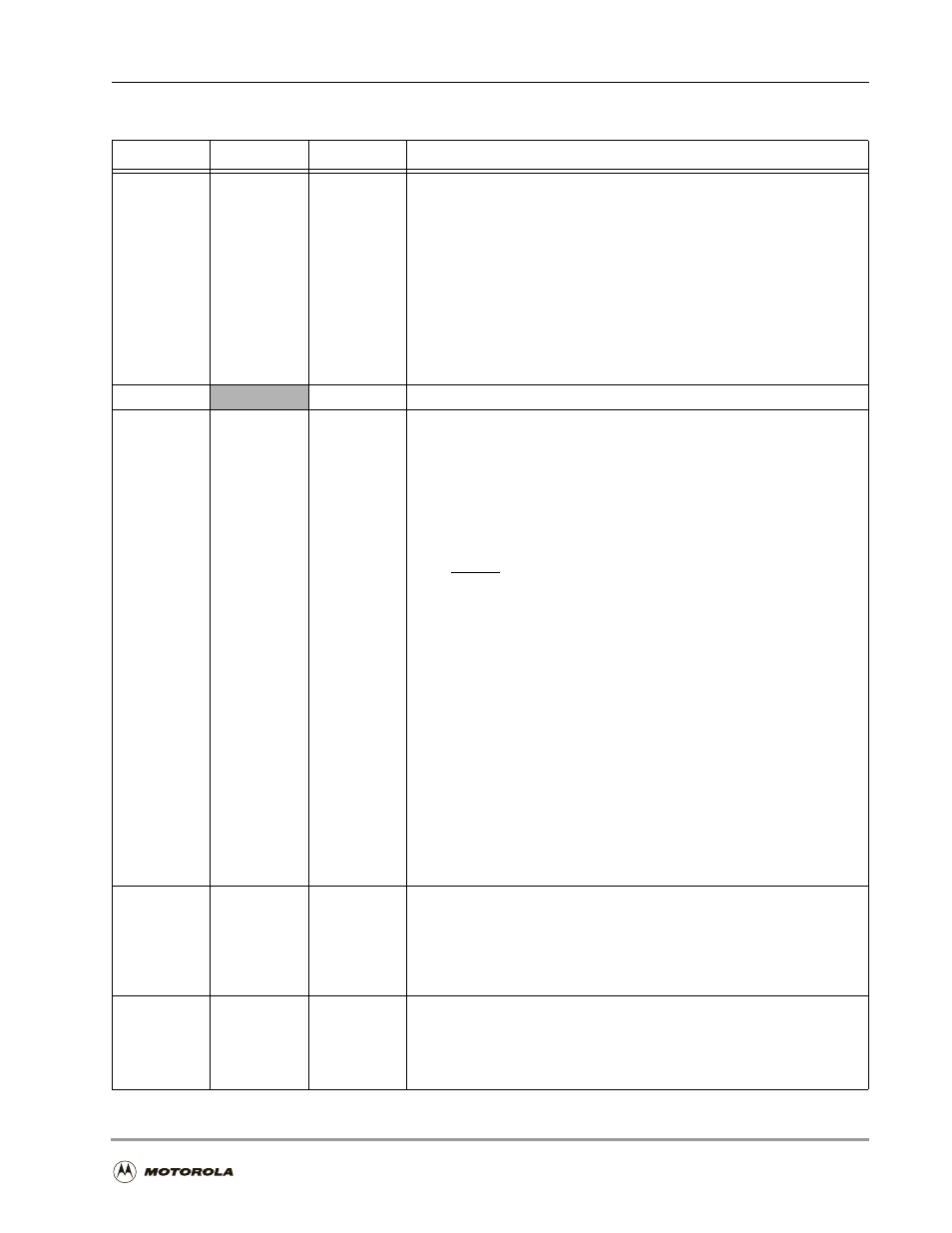

MDT

0

Master Data Transferred

Indicates the status of the latest completed PCI transaction to which the

HI32 was a PCI master. MDT is set at the end of a transaction (MARQ =

1) if the HI32 successfully transferred the master data, as defined by the

DPMC[BL] bits. Otherwise, MDT is cleared. If MARQ is set, it is sufficient

to check MDT to determine whether the HI32 transferred all master data

to the designated target. If MARQ is set and MDT is cleared, you can find

out why the transaction terminated before all the data transferred by

checking the TO, TRTY, TDIS, TAB, and MAB status bits in the DSPR.

Note:

If the Master Access Counter is disabled (DPCR[MACE] = 0),

MDT is not valid.

13

0

Reserved. Write to 0 for future compatibility.

12 HDTC

0

PCI Host Data Transfer Complete

When the receive buffer lock enable (RBLE) bit in the DSP PCI Control

Register (DPCR) is set, it indicates that the host-to-DSP data path is

empty. HDTC is set if SRRQ and MRRQ are cleared (that is, the

host-to-DSP data path is emptied by DSP56300 core reads) under one of

the following conditions:

n

A non-exclusive PCI write transaction to the HTXR terminates or

completes.

n

HLOCK is deasserted after the completion of an exclusive write

access to the HTXR. The HI32 disconnects (retry or disconnect-C)

forthcoming write accesses to the HTXR as long as HDTC is set.

Note:

The HDTC bit is not set after a read transaction initiated by the

HI32 as a PCI master.HDTC is cleared when the DSP56300 core

writes a value of one to it. The DSP56300 core can write a value

of one to HDTC only if this bit is set. When HDTC is cleared, the

HI32 responds to write PCI transactions according to the status

of the host-to-DSP data path. Hardware, software and personal

software resets clear HDTC.

Note:

Each of the bits APER, DPER, MAB, TAB, TDIS, TRTY, TO, and

HDTC are cleared by writing one to the specific bit. To assure

that only the desired bit is cleared, do not use the BSET

command. The proper way to clear these bits is to write

(MOVE(P) instruction) ones to the bits to be cleared and zeros to

all the others.

11 TO

0

PCI Time Out Termination

Indicates that an HI32-initiated PCI transaction has terminated due to the

deassertion of the bus grant after the latency timer expired. When TO is

set and DPCR[TTIE] is set, a transaction termination interrupt request is

generated. TO is cleared when the DSP56300 core writes a value of one

to it.

10

TRTY

0

PCI Target Retry

Indicates that an HI32-initiated PCI transaction has terminated with a

target-initiated retry. When TRTY is set and DPCR[TTIE] is set, a

transaction termination interrupt request is generated. TRTY is cleared

when the DSP56300 core writes a value of one to it.

Table 6-15. DSP PCI Status Register (DPSR) Bit Definitions (Continued)

Bit Number

Bit Name

Reset Value

Description