Motorola DSP56301 User Manual

Page 220

ESSI Programming Model

7

-22

DSP56301 User’s Manual

11

CKP

0

Clock Polarity

Controls which bit clock edge data and frame sync are clocked out and

latched in. If CKP is cleared, the data and the frame sync are clocked out

on the rising edge of the transmit bit clock and latched in on the falling

edge of the receive bit clock. If CKP is set, the data and the frame sync

are clocked out on the falling edge of the transmit bit clock and latched in

on the rising edge of the receive bit clock.

10

FSP

0

Frame Sync Polarity

Determines the polarity of the receive and transmit frame sync signals.

When FSP is cleared, the frame sync signal polarity is positive; that is, the

frame start is indicated by the frame sync signal going high. When FSP is

set, the frame sync signal polarity is negative; that is, the frame start is

indicated by the frame sync signal going low.

9

FSR

0

Frame Sync Relative Timing

Determines the relative timing of the receive and transmit frame sync

signal in reference to the serial data lines for word length frame sync only.

When FSR is cleared, the word length frame sync occurs together with the

first bit of the data word of the first slot. When FSR is set, the word length

frame sync occurs one serial clock cycle earlier (that is, simultaneously

with the last bit of the previous data word).

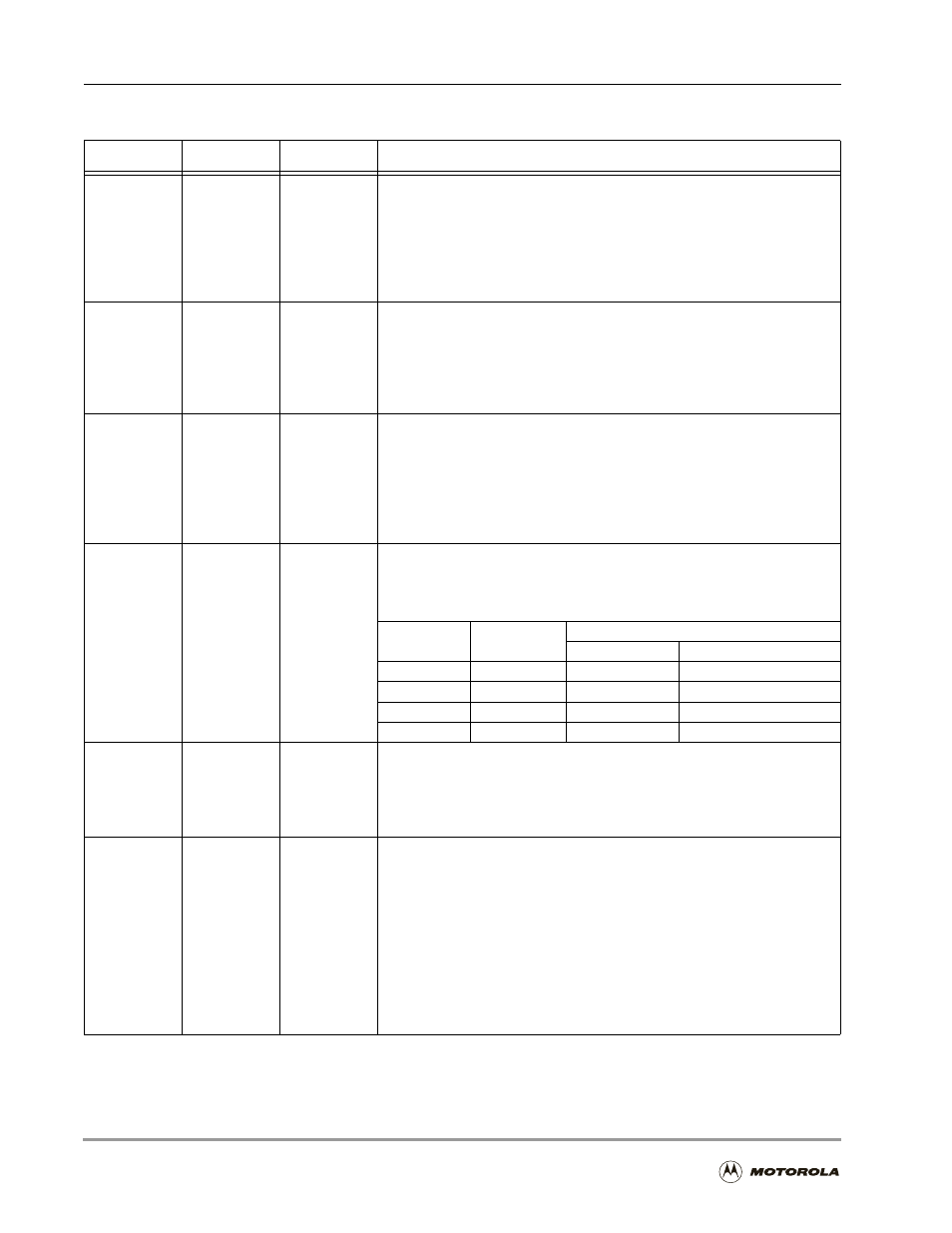

8–7

FSL[1–0]

0

Frame Sync Length

Selects the length of frame sync to be generated or recognized, as in

Figure 7-6 on page 7-24, Figure 7-9 on page 7-27, and Figure 7-10 on

page 7-27.

FSL1

FSL0

Frame Sync Length

RX

TX

0

0

word

word

0

1

word

bit

1

0

bit

bit

1

1

bit

word

6

SHFD

0

Shift Direction

Determines the shift direction of the transmit or receive shift register. If

SHFD is set, data is shifted in and out with the LSB first. If SHFD is

cleared, data is shifted in and out with the MSB first, as in Figure 7-12 on

page 7-31 and Figure 7-13 on page 7-32.

5

SCKD

0

Clock Source Direction

Selects the source of the clock signal that clocks the transmit shift register

in Asynchronous mode and both the transmit and receive shift registers in

Synchronous mode. If SCKD is set and the ESSI is in Synchronous mode,

the internal clock is the source of the clock signal used for all the transmit

shift registers and the receive shift register. If SCKD is set and the ESSI is

in Asynchronous mode, the internal clock source becomes the bit clock for

the transmit shift register and word length divider. The internal clock is

output on the SCK signal. When SCKD is cleared, the external clock

source is selected. The internal clock generator is disconnected from the

SCK signal, and an external clock source may drive this signal.

Table 7-4. ESSI Control Register B (CRB) Bit Definitions (Continued)

Bit Number

Bit Name

Reset Value

Description