12 jtag and once interface, Jtag and o, Jtag/once interface -29 – Motorola DSP56301 User Manual

Page 59: Table 2-17, 12 jtag and once interface

JTAG and OnCE Interface

Signals/Connections

2

-29

2.12

JTAG and OnCE Interface

The DSP56300 family and in particular the DSP56301 support circuit-board test strategies

based on the IEEE 1149.1 Standard Test Access Port and Boundary Scan Architecture, the

industry standard developed under the sponsorship of the Test Technology Committee of

IEEE and the JTAG. The OnCE module interfaces nonintrusively with the DSP56300 core

and its peripherals so that you can examine registers, memory, or on-chip peripherals.

Functions of the OnCE module are provided through the JTAG Test Access Port (TAP)

signals. All JTAG and OncE pins are 5 V tolerant.

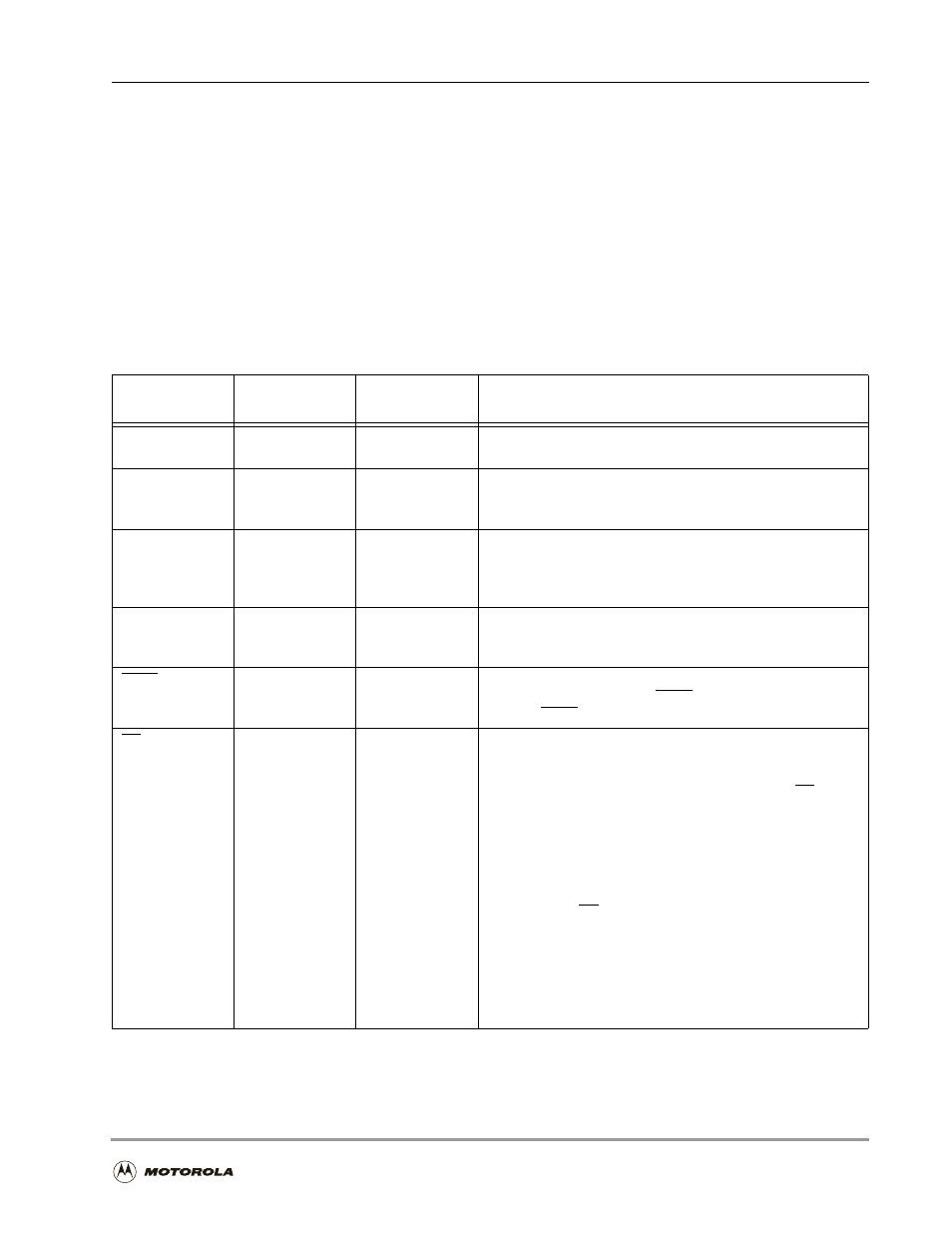

Table 2-17. JTAG/OnCE Interface

Signal Name

Type

State During

Reset

Signal Description

TCK

Input

Input

Test Clock—A test clock input signal to synchronize the

JTAG test logic.

TDI

Input

Input

Test Data Input—A test data serial input signal for test

instructions and data. TDI is sampled on the rising edge of

TCK and has an internal pull-up resistor.

TDO

Output

Tri-stated

Test Data Output—A test data serial output signal for test

instructions and data. TDO is tri-statable and is actively

driven in the shift-IR and shift-DR controller states. TDO

changes on the falling edge of TCK.

TMS

Input

Input

Test Mode Select—An input signal to sequence the test

controller’s state machine. TMS is sampled on the rising

edge of TCK and has an internal pull-up resistor.

TRST

Input

Input

Test Reset—A Schmitt-trigger input signal to asynchronously

initialize the test controller. TRST has an internal pull-up

resistor. TRST must be asserted after power up.

DE

Input/ Output

Input

Debug Event—An open-drain signal. As an input, enters the

Debug mode of operation from an external command

controller. As an output, acknowledges that the chip has

entered Debug mode. When asserted as an input, DE causes

the DSP56300 core to finish the executing instruction, save

the instruction pipeline information, enter the Debug mode,

and wait for commands to be entered from the debug serial

input line. This signal is asserted as an output for three clock

cycles when the chip enters Debug mode as a result of a

debug request or as a result of meeting a breakpoint

condition. The DE has an internal pull-up resistor.

This is not a standard part of the JTAG TAP controller. The

signal connects directly to the OnCE module to initiate Debug

mode directly or to provide a direct external indication that

the chip has entered the debug mode. All other interface with

the OnCE module must occur through the JTAG port.