2 timer pulse (mode 1), Timer pulse (mode 1) -8, Pulse mode (trm = 1) -8 – Motorola DSP56301 User Manual

Page 270

Operating Modes

9

-8

DSP56301 User’s Manual

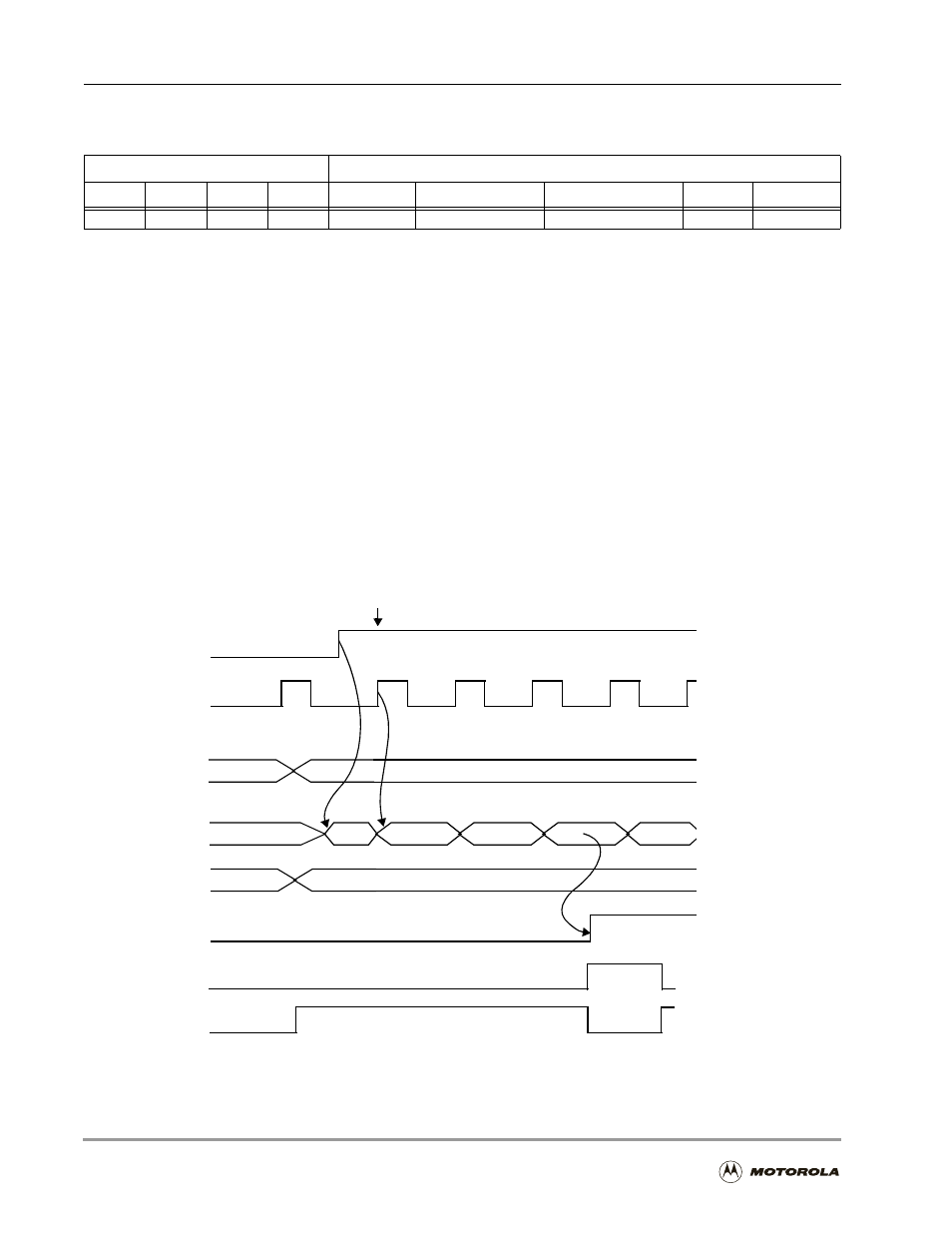

9.3.1.2 Timer Pulse (Mode 1)

In Mode 1, the timer generates an external pulse on its TIO signal when the timer count

reaches a pre-set value. The TIO signal is loaded with the value of the TCSR[INV] bit. When

the counter matches the TCPR value, TCSR[TCF] is set and a compare interrupt is generated

if the TCSR[TCIE] bit is set. The polarity of the TIO signal is inverted for one timer clock

period. If TCSR[TRM] is set, the counter is loaded with the TLR value on the next timer

clock and the count is resumed. If TCSR[TRM] is cleared, the counter continues to increment

on each timer clock. This process repeats until TCSR[TE] is cleared (disabling the timer).

The TLR value in the TCPR sets the delay between starting the timer and generating the

output pulse. To generate successive output pulses with a delay of X clock cycles between

signals, set the TLR value to X/2 and set the TCSR[TRM] bit. This process repeats until the

timer is disabled.

Bit Settings

Mode Characteristics

TC3

TC2

TC1

TC0

Mode

Name

Function

TIO

Clock

0

0

0

1

1

Timer Pulse

Timer

Output

Internal

Figure 9-5. Pulse Mode (TRM = 1)

Mode 1 (internal clock): TRM = 1

N = write preload

M = write compare

TE

Clock

(CLK/2 or prescale CLK)

TLR

TCPR

TCF (Compare Interrupt if TCIE = 1)

Counter (TCR)

first event

M

0

N

N + 1

M

N

N + 1

N

pulse width =

timer clock

period

TIO pin (INV = 0)

TIO pin (INV = 1)