Motorola DSP56301 User Manual

Page 102

Bus Interface Unit (BIU) Registers

4

-28

DSP56301 User’s Manual

7

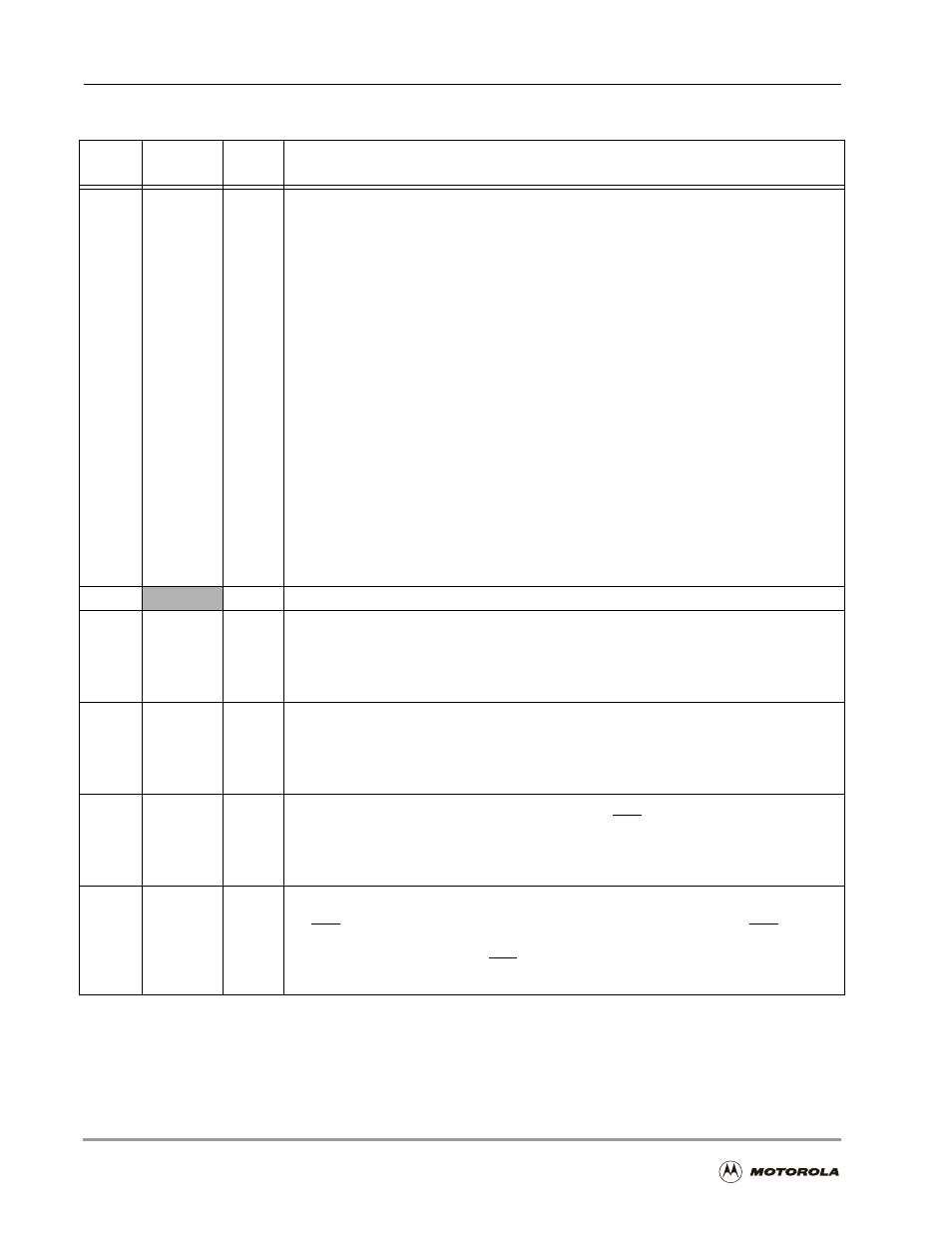

BPAC

0

Bus Packing Enable

Enables/disables the internal packing/unpacking logic. When BPAC is set, packing is

enabled. In this mode each DMA external access initiates three external accesses to an

8-bit wide external memory (the addresses for these accesses are DAB, then DAB + 1 and

then DAB + 2). Packing to a 24-bit word (or unpacking from a 24-bit word to three 8-bit

words) is done automatically by the expansion port control hardware. The external

memory should reside in the eight Least Significant Bits (LSBs) of the external data bus,

and the packing (or unpacking for external write accesses) occurs in “Little Endian” order

(that is, the low byte is stored in the lowest of the three memory locations and is

transferred first; the middle byte is stored/transferred next; and the high byte is

stored/transferred last). When this bit is cleared, the expansion port control logic assumes

a 24-bit wide external memory.

Notes: 1.

BPAC is used only for DMA accesses and not core accesses.

2.

To ensure sequential external accesses, the DMA address should advance

three steps at a time in two-dimensional mode with a row length of one and

an offset size of three. For details, refer to Motorola application note,

APR23/D,

Using the DSP56300 Direct Memory Access Controller.

3.

To prevent improper operation, DMA address + 1 and DMA

address + 2 should not cross the AAR bank borders.

4.

Arbitration is not allowed during the packing access (that is, the three

accesses are treated as one access with respect to arbitration, and the bus

mastership is not released during these accesses).

6

0

Reserved. Write to 0 for future compatibility.

5

BYEN

0

Bus Y Data Memory Enable

A read/write control bit that enables/disables the AA pin and logic during external Y data

space accesses. When set, BYEN enables the comparison of the external address to the

BAC bits during external Y data space accesses. If BYEN is cleared, no address

comparison is performed.

4

BXEN

0

Bus X Data Memory Enable

A read/write control bit that enables/disables the AA pin and logic during external X data

space accesses. When set, BXEN enables the comparison of the external address to the

BAC bits during external X data space accesses. If BXEN is cleared, no address

comparison is performed.

3

BPEN

0

Bus Program Memory Enable

A read/write control bit that enables/disables the AA/RAS pin and logic during external

program space accesses. When set, BPEN enables the comparison of the external

address to the BAC bits during external program space accesses. If BPEN is cleared, no

address comparison is performed.

2

BAAP

0

Bus Address Attribute Polarity

A read/write Bus Address Attribute Polarity (BAAP) control bit that defines whether the

AA/RAS signal is active low or active high. When BAAP is cleared, the AA/RAS signal is

active low (useful for enabling memory modules or for DRAM Row Address Strobe). If

BAAP is set, the appropriate AA/RAS signal is active high (useful as an additional address

bit).

Table 4-11. Address Attribute Registers (AAR[0–3]) Bit Definitions (Continued)

Bit

Number

Bit Name

Reset

Value

Description