Motorola DSP56301 User Manual

Page 150

HI32 DSP-Side Programming Model

6

-32

DSP56301 User’s Manual

23–22

Cont.

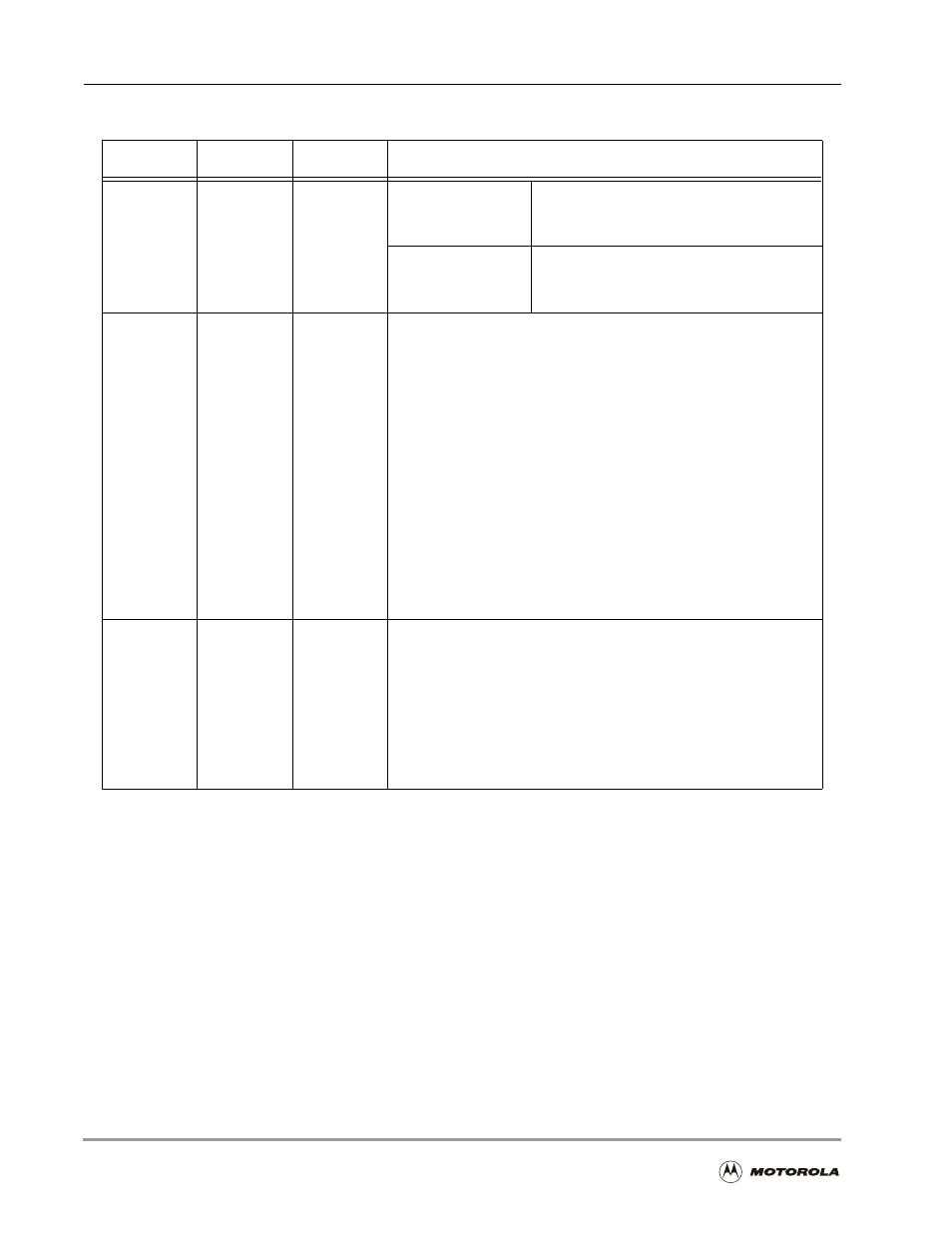

FC[1–0]

Cont.

0

DPMC[FC] = $1 or $2 The three least significant PCI data bytes from

the HAD[23–0] pins are transferred to the

DRXR to be read by the DSP56300 core.

DPMC[FC] = $3

The three most significant PCI data bytes from

the HAD[31–8] pins are transferred to the

DRXR to be read by the DSP56300 core.

21–16

BL[5–0]

0

PCI Data Burst Length

Control the PCI data burst length. The value of the BL[5–0] bits is the

desired number of accesses in the burst, minus one. In PCI mode

(DCTR[HM]

=

$1), when the DSP56300 core writes to the DPAR, the

master access counter is initialized with the value of BL[5–0]. The

burst length can be programmed from 1 (BL = $00) to 64 (BL = $3F)

accesses. If the master access counter is enabled (MACE = 1 in the

DPCR) and the HI32 is the active PCI master, the value of the counter

decrements after each data cycle in which data is transferred (that is,

a data phase) until the counter value reaches $00. Then the HI32 PCI

master executes one more data phases and terminates the

transaction. A transaction can be terminated before the counter

reaches $00—for example, via a target-initiated transaction

termination, the bus grant is taken, or the DSP56300 core writes a

value of one to MTT. The value of the counter at the end of a

transaction is indicated by the RDC[5–0] bits in the DSP PCI Status

Register (DPSR).

15–0

AR[31–16]

0

DSP PCI Transaction Address (High)

The two most significant bytes of the 32-bit PCI transaction address.

The two least significant bytes reside in the DPAR (see Section

6.7.4,

DSP PCI Address Register (DPAR), on page 6-33). In PCI

mode (DCTR[HM] = $1),when the DSP56300 core writes to the

DPAR, the PCI ownership is requested. When the request is granted,

the HI32 initiates a PCI transaction. The full 32-bit address

(AR[31–16] from the DPMC and AR[15–0] from the DPAR) is driven

to the HAD[31–0] pins during the PCI address phase.

Table 6-12. DSP PCI Master Control Register (DMPC) Bit Definitions (Continued)

Bit Number

Bit Name

Reset Value

Description