Motorola DSP56301 User Manual

Page 319

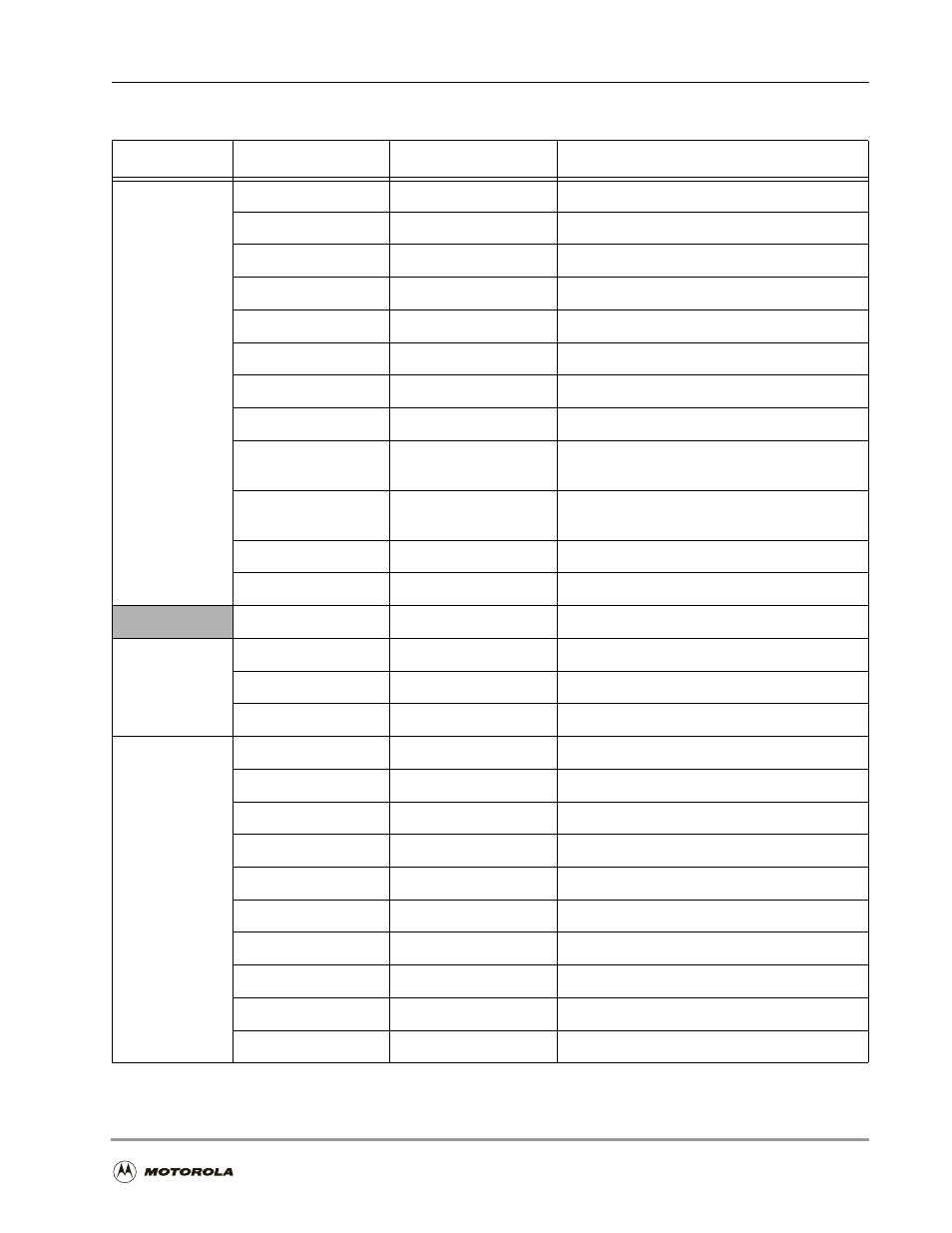

Internal I/O Memory Map

Programming Reference

B

-7

ESSI 1

$FFAC

$FFFFAC

ESSI 1 Transmit Data Register 0 (TX10)

$FFAB

$FFFFAB

ESSI 1 Transmit Data Register 1 (TX11)

$FFAA

$FFFFAA

ESSI 1 Transmit Data Register 2 (TX12)

$FFA9

$FFFFA9

ESSI 1 Time Slot Register (TSR1)

$FFA8

$FFFFA8

ESSI 1 Receive Data Register (RX1)

$FFA7

$FFFFA7

ESSI 1 Status Register (SSISR1)

$FFA6

$FFFFA6

ESSI 1 Control Register B (CRB1)

$FFA5

$FFFFA5

ESSI 1 Control Register A (CRA1)

$FFA4

$FFFFA4

ESSI 1 Transmit Slot Mask Register A

(TSMA1)

$FFA3

$FFFFA3

ESSI 1 Transmit Slot Mask Register B

(TSMB1)

$FFA2

$FFFFA2

ESSI 1 Receive Slot Mask Register A (RSMA1)

$FFA1

$FFFFA1

ESSI 1 Receive Slot Mask Register B (RSMB1)

$FFA0

$FFFFA0

Reserved

PORT E

$FF9F

$FFFF9F

Port E Control Register (PCRE)

$FF9E

$FFFF9E

Port E Direction Register (PRRE)

$FF9D

$FFFF9D

Port E GPIO Data Register (PDRE)

SCI

$FF9C

$FFFF9C

SCI Control Register (SCR)

$FF9B

$FFFF9B

SCI Clock Control Register (SCCR)

$FF9A

$FFFF9A

SCI Receive Data Register - High (SRXH)

$FF99

$FFFF99

SCI Receive Data Register - Middle (SRXM)

$FF98

$FFFF98

SCI Recieve Data Register - Low (SRXL)

$FF97

$FFFF97

SCI Transmit Data Register - High (STXH)

$FF96

$FFFF96

SCI Transmit Data Register - Middle (STXM)

$FF95

$FFFF95

SCI Transmit Data Register - Low (STXL)

$FF94

$FFFF94

SCI Transmit Address Register (STXA)

$FF93

$FFFF93

SCI Status Register (SSR)

Table B-2. Internal I/O Memory Map (X Data Memory) (Continued)

Peripheral

16-Bit Address

24-Bit Address

Register Name