Motorola DSP56301 User Manual

Page 198

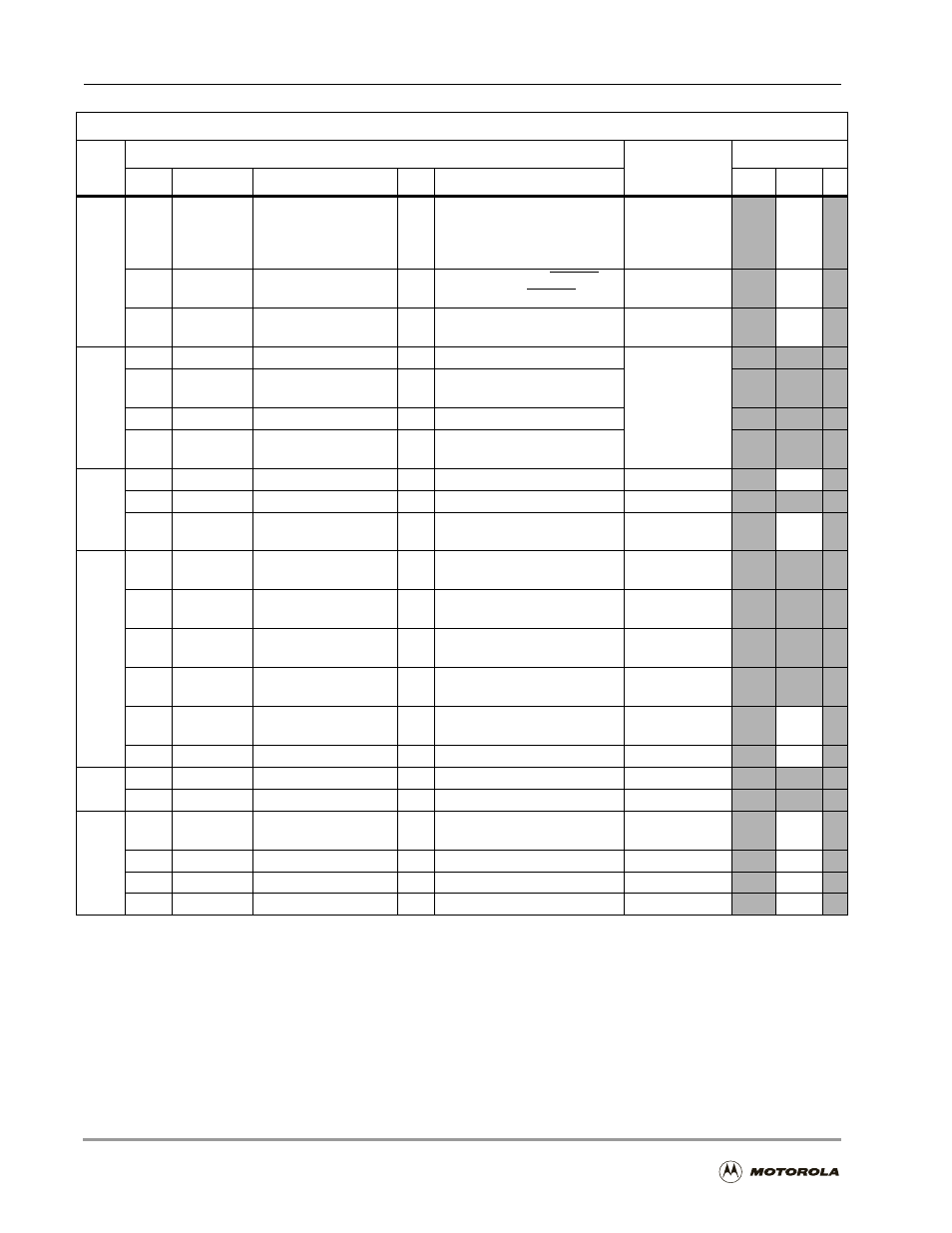

HI32 Programming Model/Quick Reference

6

-80

DSP56301 User’s Manual

CCMR

CSTR

cont.

29

RMA

Received Master Abort

0

1

HI32 has not received a

master-abort event

HI32 master, terminates a

transaction with master-abort

cleared by

writing 1

-

0

-

30

SSE

Signaled System Error

0

1

HI32 not asserted HSERR

HI32 asserted HSERR

cleared by

writing 1

-

0

-

31

DPE

Detected Parity Error

0

1

no parity error detected

parity error detected

cleared by

writing 1

-

0

-

CRID

CCCR

7-0

RID[7–0]

Revision ID

See Table6-26

-

-

-

15-8

PI[7–0]

PCI Device Program

Interface

-

-

-

23-16

SC[7–0]

PCI Device Sub-Class

-

-

-

31-24

BC[7–0]

PCI Device Base

Class

-

-

-

CLAT

CHTY

CCLS

15-8

LT[7–0]

Latency Timer

-

$00

-

23-16

HT[7–0]

Header Type

$0

hardwired $0

-

-

-

7–0

CLS[7–0] Cache Line

Specify system cache line

size in units of 32-bit words

0

CBMA

0

MSI

Memory Space

Indicator

0

HI32 is a memory-mapped

agent

hardwired 0

-

-

-

2-1

MS[1–0]

Memory Space

$0 32 bits wide and mapping can

be done anywhere

hardwired $0

-

-

-

3

PF

Prefetch

0

HI32 data is not pre-fetchable

(in the PCI sense)

hardwired 0

-

-

-

15-4

PM[15–4]

Memory Base Address

Low

$00 64 Kbytes occupancy of PCI

memory space

hardwired $00

-

-

-

31-16

PM[31–16] Memory Base Address

High

-

$0000

-

23-15

GB[10–3]

UBM Base Address

-

$00

-

CSID

31–16 SID[15–0]

Subsystem ID

-

-

-

15–8

SVID[15–0] Subsystem Vendor ID

-

-

-

CILP

7-0

IP[7–0]

Interrupt Line

PCI interrupt line routing

information

15-8

IL[7–0]

Interrupt Line

$01 INTA is supported

hardwired $01

23-16

MG[7–0]

MAX_GNT

$00 Min Grant

hardwired $00

31-24

ML[7–0]

MAX_LAT

$00 Max Latency

hardwired $00

1.

STRQ. MTRQ are zero in the personal software reset state.

HI32 Registers—Quick Reference

Reg

Bit

Comments

Reset Type

Num

Mnemonic

Name

Val

Function

HS

PH

PS