Motorola DSP56301 User Manual

Page 188

Host-Side Programming Model

6

-70

DSP56301 User’s Manual

6.8.11

Memory Space Base Address Configuration Register (CBMA)

r

A PCI-standard read/write register mapped into the PCI configuration space in PCI mode or

in mode 0 (HM

=

$1 or $0). The CBMA is accessed if a configuration read/write command is

in progress and the PCI address is $10. The CBMA controls the HI32 mapping into the PCI

memory space and the Universal Bus mode space. In Self-Configuration mode (DCTR[HM]

= $5), the DSP56300 core can indirectly access the CBMA (see Section 6.5.5,

Self-Configuration Mode (DCTR[HM] = $5), on page 6-16). The CBMA is written in

accordance with the byte enables. Byte lanes that are not enabled are not written and the

corresponding bits remain unchanged. The host can access CBMA only when the HI32 is in

PCI mode (HM

≠

$1).

31

30

29

28

27

26

25

24

23

22

21

20

19

18

17

16

PM31 PM30 PM29 PM28 PM27 PM26 PM25 PM24 PM23/

GB10

PM22/

GB9

PM21/

GB98

PM20/

GB7

PM19/

GB6

PM18/

GB5

PM17/

GB4

PM16/

GB3

15

14

13

12

11

10

9

8

7

6

5

4

3

2

1

0

PM15 PM14 PM13 PM12 PM11 PM10 PM9

PM8

PM7

PM6

PM5

PM4

PF

MS1

MS0

MSI

Hardwired to zero

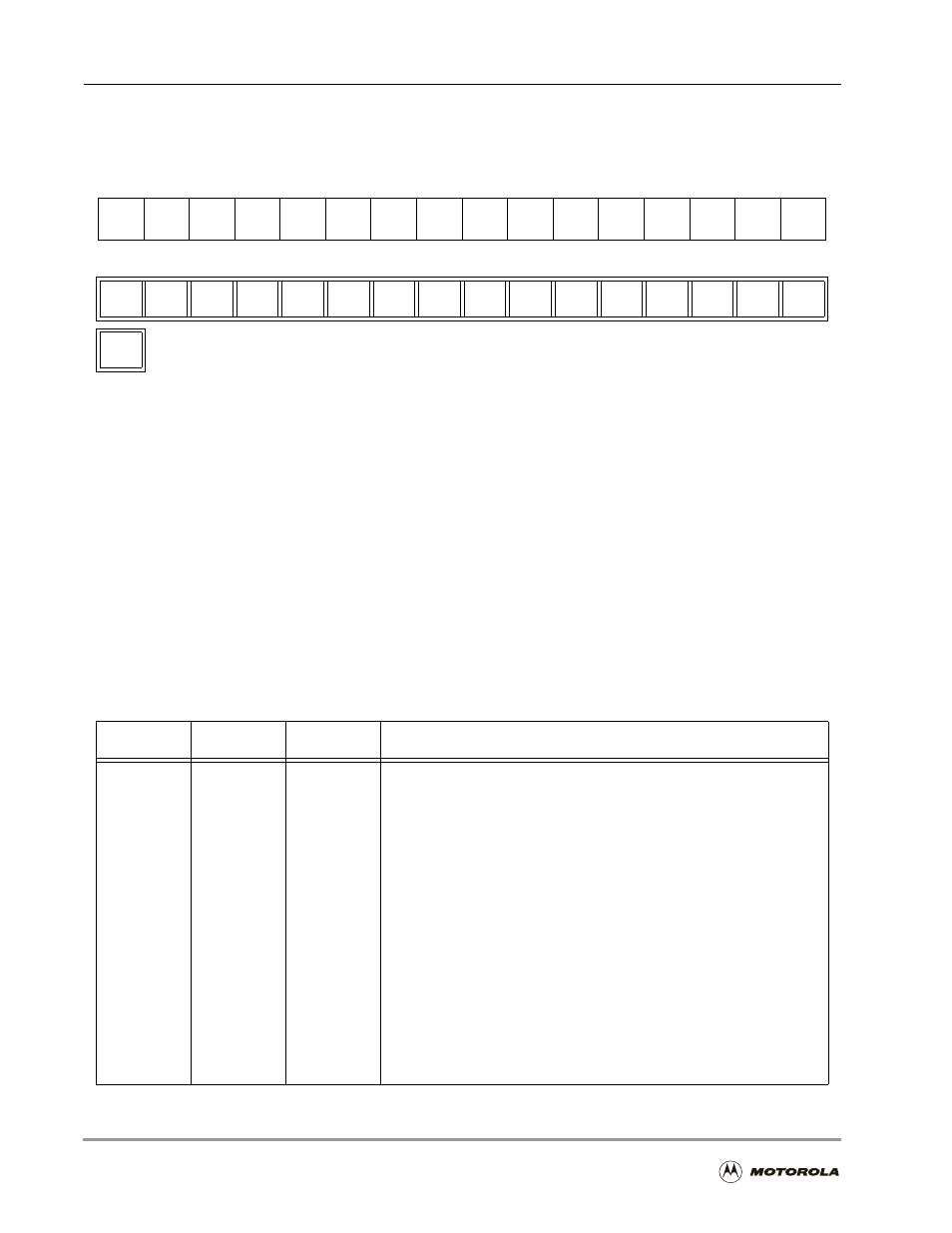

Figure 6-20. Memory Space Base Address Configuration Register (CBMA)

Table 6-29. Memory Space Base Address Configuration Register (CBMA)

Bit Definitions

Bit Number

Bit Name

Reset Value

Description

31–16

23–16

PM[31–16]

GB[10–3]

0

Memory Base Address High/Low

Defines the HI32 base address when it is mapped into the PCI memory

space. PM[15–4] are hardwired to zero, and the PCI master can write to

PM[31–16] during system configuration. The HI32 target occupies

16384 32-bit words of the PCI memory space. The HI32 is selected by

the 20 most significant PCI address pins HAD[31–12]. The twelve least

significant address pins HAD[11–0] select the HI32 registers on the

host side (see Figure 6-2 on page 6-19). The personal hardware reset

clears PM[31–16].

Universal Bus Mode Base Address

Defines the HI32 base address when it is mapped into the Universal

Bus mode space. The remaining CBMA bits are ignored in the

Universal Bus modes. The HI32 slave occupies eight locations in the

Universal Bus mode space. The HI32 is selected by the eight most

significant address pins HA[10–3]. The three least significant address

pins HA[2–0] select the HI32 registers on the host side. The personal

hardware reset clears GB[10–3].