Motorola DSP56301 User Manual

Page 178

Host-Side Programming Model

6

-60

DSP56301 User’s Manual

If TWSD is cleared, the HI32 is the selected PCI target (DCTR[HM]

=

$1) in a write data

phase to the HCVR. It inserts PCI wait states if a host command is pending (HC = 1). Wait

states are inserted until the pending host command is serviced. Up to eight wait states can be

inserted before a target-initiated transaction termination (disconnect-C/Retry) is generated. In

a Universal Bus mode write to the HCVR, the HI32 inserts wait states if a host command is

pending (HC = 1). Wait states are inserted until the pending host command is serviced.

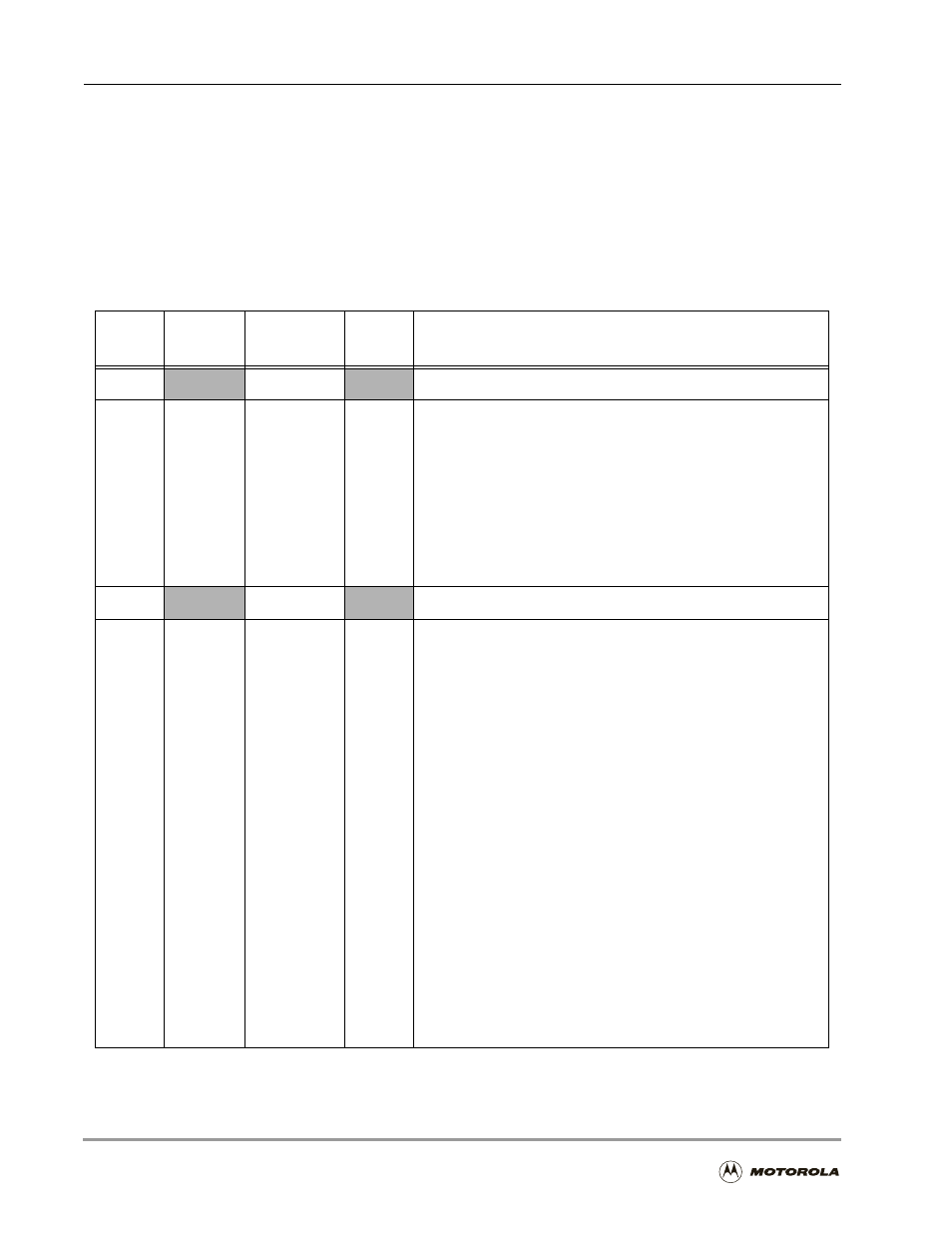

Table 6-24. Host Command Vector Register (HCVR) Bit Definitions

Bit

Number

Bit Name

Reset Value

Mode

Description

31–16

0

Reserved. Write to zero for future compatibility.

15

HNMI

0

UBM

PCI

Host Non-Maskable Interrupt

Used by the host processor to force the generation of the host

command as a non-maskable interrupt request. If HNMI and HC

are set, the host command interrupt is processed with the highest

priority, regardless of the current HI32 interrupt priority (as written

in the DSP56300 Peripheral Priority Register (IPRP)). If HNMI is

cleared and HC is set, the host command interrupt is processed in

accordance with the priority programmed in the IPRPand can be

disabled by clearing DCTR[HCIE]. The personal hardware reset

clears HNMI.

14–8

0

Reserved. Write to zero for future compatibility.

7–1

HV[6–0]

Programmable

UBM

PCI

Host Command Vector

Select the host command interrupt address. When the DSP56300

core interrupt control logic recognizes the host command interrupt,

the starting address of the executed interrupt is 2

×

(HV[6–0]).

The host processor can select any of the 128 possible interrupt

routine starting addresses in the DSP by writing the interrupt

routine starting address divided by two into HV. This means that

the host processor can force any of the existing interrupt routines

(SSI, Timer, IRQA, IRQB, and so on) and can use any of the

reserved or otherwise unused starting addresses if they have been

pre-programmed in the DSP. The host processor can force

non-maskable interrupts of the DSP56300 core by setting the host

non-maskable interrupt (HNMI) bit in the HCVR. When the HI32

command interrupt logic recognizes that HNMI is set, the host

command interrupt is processed with the highest priority,

regardless of the current HI32 interrupt priority (as written in the

DSP56300 Peripheral Priority Register (IPRP)).

CAUTION: HV[6–0] should not be used with a value of zero, the

reset location, because this location is normally programmed with

a JMP instruction. Doing so causes an improper short interrupt.

The personal hardware reset sets HV to the default host command

vector, which is programmable).