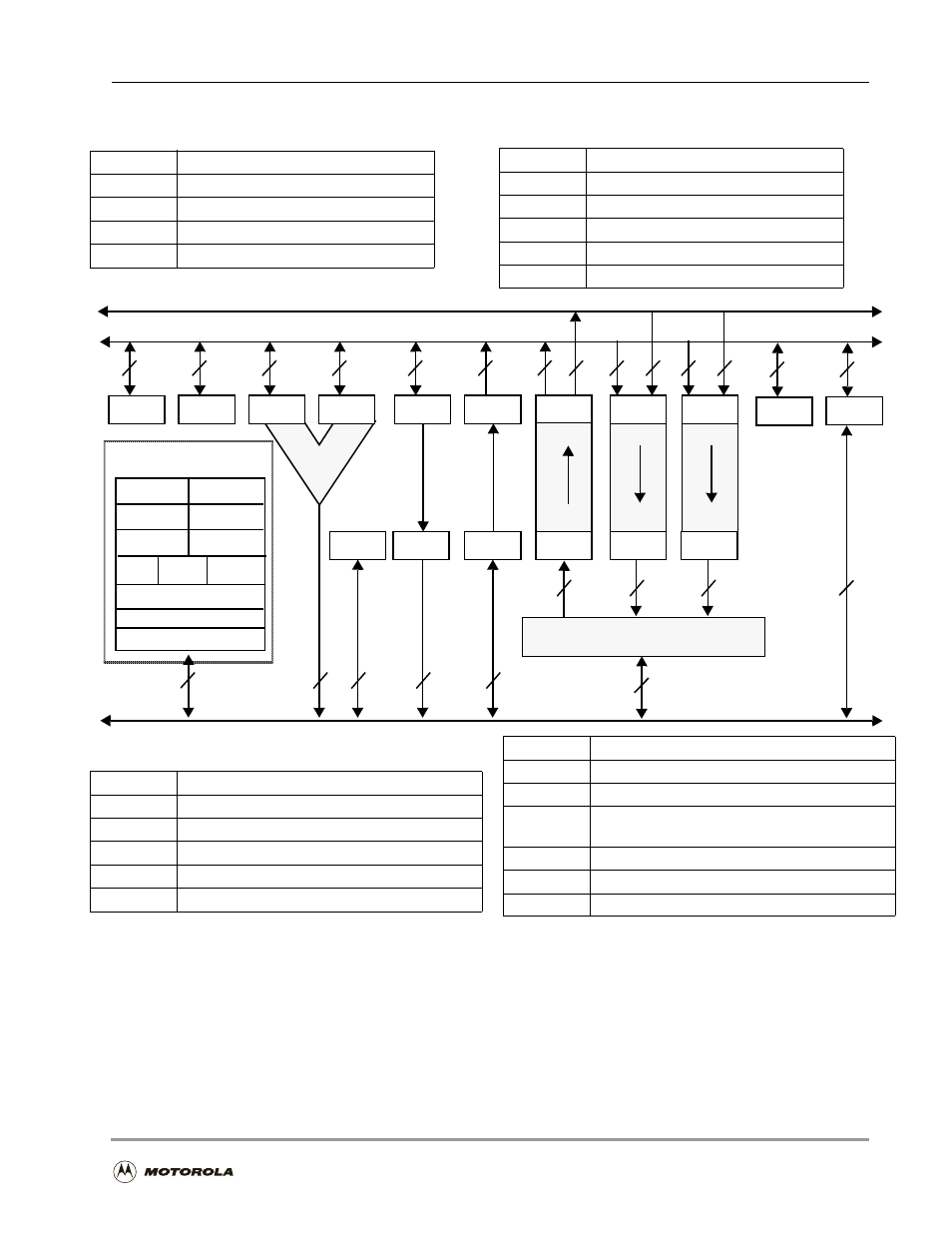

Hi32 block diagram -5, Dsp-side registers, Figure 6-1. hi32 block diagram – Motorola DSP56301 User Manual

Page 123: Host bus, Host-side, Registers

Overview

Host Interface (HI32)

6

-5

Figure 6-1. HI32 Block Diagram

In Self-Configuration mode (DCTR[HM] = $5), the DSP56300 core can indirectly write all

registers in the PCI Configuration Space but the CDID/DVID register. The HI32 cannot read

any of the registers in its configuration space. Host processors can use standard host processor

instructions and addressing modes to communicate with the HI32 registers. The host

processor can be any of a number of industry-standard microcomputers or microprocessors,

CDID/CVID

Device ID/Vendor ID Configuration Register

CSTR/CCMR

Status/Command Configuration Register

CCCR/CRID

Class Code/Revision ID Configuration Register

CHTY/CLAT/

CCLS

Header Type/Latency Timer Configuration Register

Cache Line Size Configuration Register

CBMA

Memory Space Base Address Configuration Register

CSID

Subsystem Vendor ID Configuration Register

CILP

Interrupt Line-Interrupt Pin Configuration Register

24

DSP DMA Data Bus

DSP Global Data Bus

HOST Bus

32

32

24

24

DPCR

24

DPMC

24

DPAR

24

DCTR

24

24

24

24

24

24

32

32

32

32

HCTR

HCVR

DSR

DTXM

DTXS

PCI Configuration Space

DPSR

HSTR

HTXR

HRXS

data transfer format converter

24

DRXR

HRXM

24

24

6

w

o

rd

s

deep

8

w

o

rd

s

deep

6

w

o

rd

s

deep

24

24

DATH

DIRH

24

DSP-Side Registers

DCTR

DSP Control Register

DPCR

DSP PCI Control Register

DPMC

DSP PCI Master Control Register

DPAR

DSP PCI Address Register

DSR

DSP Status Register

DPSR

DSP PCI Status Register

DRXR

DSP Receive Data Register

DTXM

DSP Master Transmit Data Register

DTXS

DSP Slave Transmit Data Register

DIRH

DSP Host Port GPIO Direction Register

DATH

DSP Host Port GPIO Data Register

Host-Side

Registers

HCTR

Host Interface Control Register

HSTR

Host Interface Status Register

HCVR

Host Command Vector Register

HRXM

Host Master Receive Data Register

HRXS

Host Slave Receive Data Register

HTXR

Host Transmit Data Register

CDID

CVID

CSTR

CCMR

CCCR

CRID

CHTY CLAT CCLS

CBMA

CSID

CILP

Note:

As the PCI master, the HI32 uses the HRXM to output data. The host bus cannot access this register.