Output clock with skew elimination – Motorola DSP56301 User Manual

Page 21

DSP56300 Core Features

Overview

1

-5

n

Phase Lock Loop (PLL)—Allows change of low power Divide Factor (DF) without

loss of lock

n

Output clock with skew elimination

n

Hardware debugging support

— On-Chip Emulation (OnCE) module

— Joint Action Test Group (JTAG) Test Access Port (TAP) port

— Address Trace mode reflects internal Program RAM accesses at the external port

n

On-chip memories:

— Program RAM, instruction cache, X data RAM, and Y data RAM sizes are

programmable:

— 192 or 3 K

×

24-bit bootstrap ROM, depending on the DSP56301 revision

n

Off-chip memory expansion:

— Data memory expansion to two 16 M

×

24-bit word memory spaces in 24-Bit mode

or two 64 K

×

16-bit memory spaces in Sixteen-Bit Compatibility mode

— Program memory expansion to one 16 M

×

24-bit words memory space in

24-Bit mode or 64 K

×

16-bit in Sixteen-Bit Compatibility mode

— External memory expansion port

— Chip Select Logic for glueless interface to SRAMs

— On-chip DRAM Controller for glueless interface to DRAMs

n

On-chip peripheral support:

— 32-bit parallel PCI/Universal Host Interface (HI32), PCI Rev. 2.1 compliant with

glueless interface to other DSP563xx buses

— ISA interface requires only 74LS45-style buffer

— Two Enhanced Synchronous Serial Interfaces (ESSI0 and ESSI1)

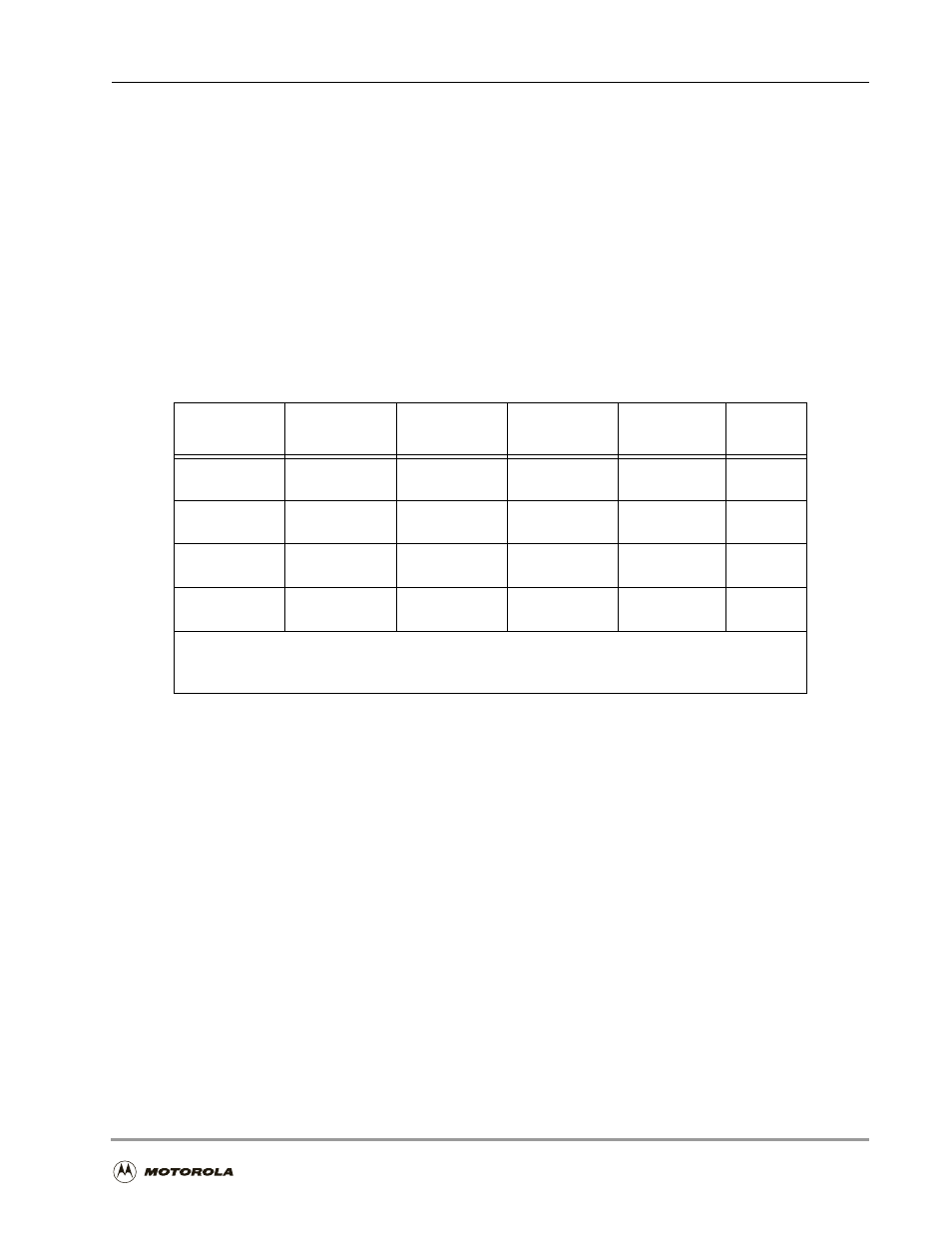

Program RAM

Size

Instruction

Cache Size

X Data RAM

Size

Y Data RAM

Size

Instruction

Cache

1

Switch

Mode

2

4096

×

24-bit

0

2048

×

24-bit

2048

×

24-bit

disabled

(CE = 0)

disabled

(MS = 0)

3072

×

24-bit

1024

×

24-bit

2048

×

24-bit

2048

×

24-bit

enabled

(CE = 1)

disabled

(MS = 0)

2048

×

24-bit

0

3072

×

24-bit

3072

×

24-bit

disabled

(CE = 0)

enabled

(MS = 1)

1024

×

24-bit

1024

×

24-bit

3072

×

24-bit

3072

×

24-bit

enabled

(CE = 1)

enabled

(MS = 1)

1.

Controlled by the Cache Enable (CE) bit in the Status Register (SR)

2.

Controlled by the Memory Select (MS) bit in the Operating Mode Register (OMR)