B-21, Figure b-21, Essi control register b (crb) – Motorola DSP56301 User Manual

Page 345: Essi, Figure b-21. essi control register b (crb), Programming sheets, B-33, Application: date: programmer

Programming Sheets

Programming Reference

B

-33

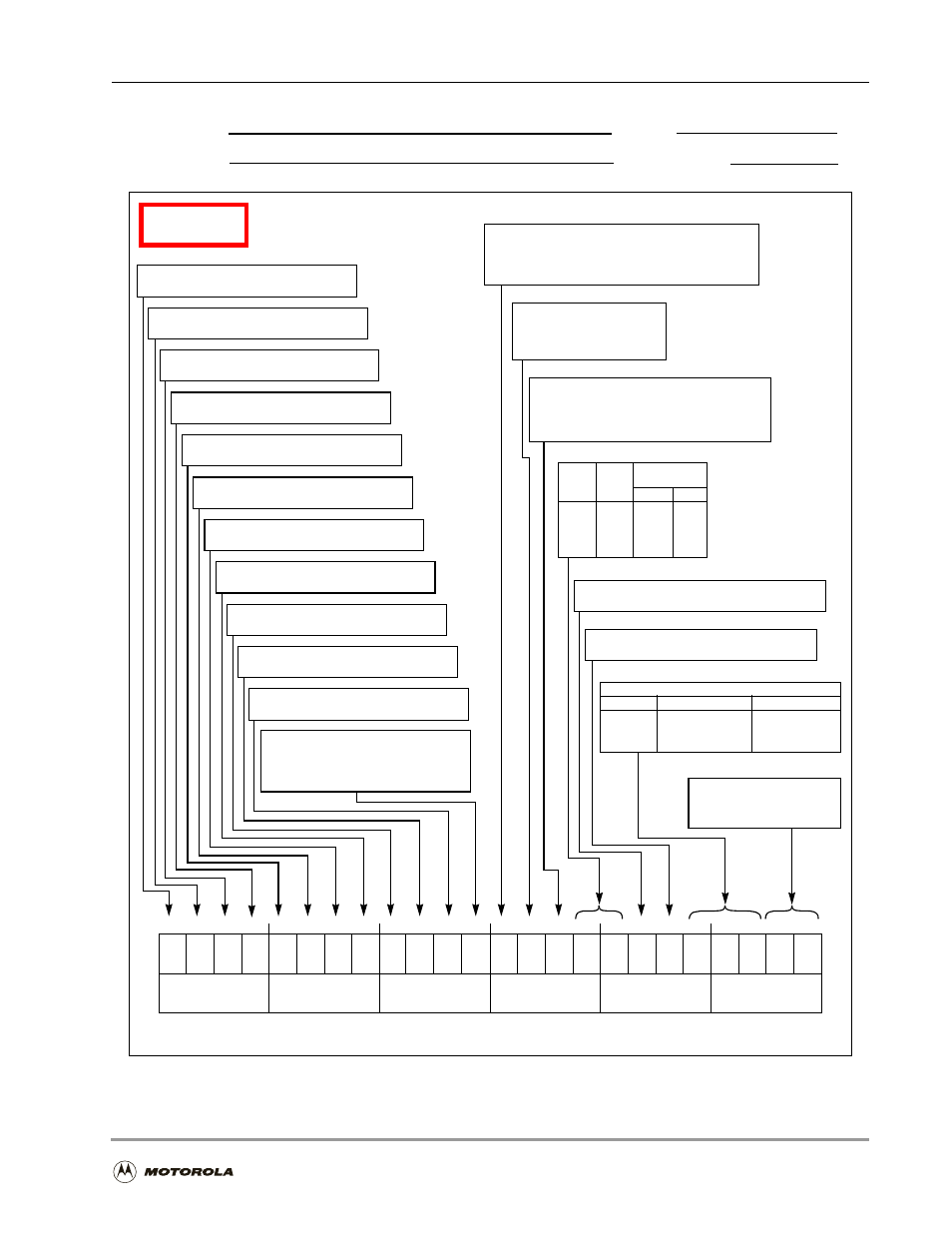

Figure B-21. ESSI Control Register B (CRB)

Application:

Date:

Programmer:

Sheet 2 of 3

ESSI

15 14 13 12 11 10

9

8

7

6

5

4

3

2

1

0

FSL0

SCKD SCD2 SCD1 SCD0 OF1

OF0

19 18 17 16

23 22 21 20

TIE

RIE

RLIE

REIE

SHFD

TEIE

TE0

TE1

TE2

MOD SYN CKP

TLIE

RE

FSP

FSR FSL1

ESSI Control Register B (CRBx)

ESSI0—X:$FFFFB6 Read/Write

ESSI1—X:$FFFFA6 Read/Write

Reset = $000000

Receive Exception Interrupt Enable

0 = Disable 1 = Enable

Transmit 2 Enable (SYN=1 only)

0 = Disable 1 = Enable

Mode Select

0 = Normal

1 = Network

Transmit 1 Enable (SYN=1 only)

0 = Disable 1 = Enable

Transmit Interrupt Enable

0 = Disable 1 = Enable

Receive Interrupt Enable

0 = Disable 1 = Enable

Transmit Last Slot Interrupt Enable

0 = Disable 1 = Enable

Receive Last Slot Interrupt Enable

0 = Disable 1 = Enable

Transmit Exception Interrupt Enable

0 = Disable 1 = Enable

Transmit 0 Enable

0 = Disable 1 = Enable

Receiver Enable

0 = Disable 1 = Enable

Clock Polarity

0 = out on rising/in on falling

1 = in on rising/out on falling

Sync/Async Control

0 = Asynchronous

1 = Synchronous

Frame Sync Polarity

0 = high level (positive)

1 = low level (negative)

Frame Sync Relative Timing

0 = with first data bit

1 = 1 clock cycle earlier than first data bit

FSL1

FSL0

Frame Sync

Length

TX

RX

0

0

Word

Word

0

1

Bit

Word

1

0

Bit

Bit

1

1

Word

Bit

Shift Direction

0 = MSB First 1 = LSB First

Clock Source Direction

0 = External Clock 1 = Internal Clock

Serial Control Direction Bits (see Table 7-2)

Pin

SCDx = 0 (Input)

SCDx = 1 (Output)

SC0

Rx Clk

Flag 0

SC1

Rx Frame Sync

Flag 1

SC2

Tx Frame Sync

Tx, Rx Frame Sync

Output Flag x

If SYN = 1 and SCD1 = 1

OFx

→

SCx Pin

(Tx & Rx transfer together or not)

(clk edge data & Frame Sync clocked out/in)

(WL Frame Sync only)