Motorola DSP56301 User Manual

Page 143

HI32 DSP-Side Programming Model

Host Interface (HI32)

6

-25

15

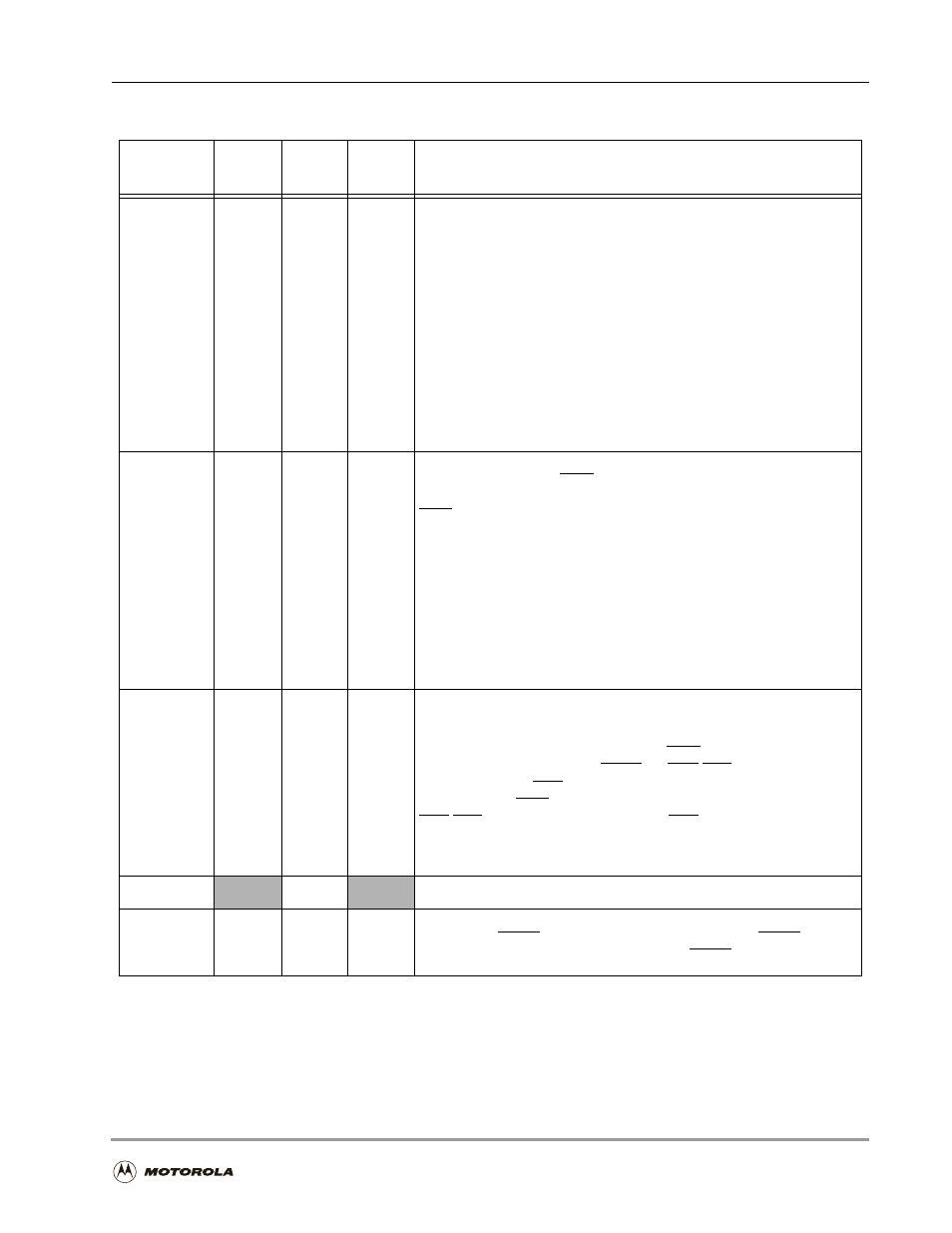

HTAP

0

UB

Host Transfer Acknowledge Polarity

Controls the polarity of the HTA pin when the HI32 is in a Universal Bus

mode (DCTR[HM]

=

$2 or $3). If HTAP is cleared, the HTA pin is active

high and the HI32 requests to extend the access by driving the HTA pin

low (that is, deasserted). If HTAP is set, the HTA pin is active low and

the HI32 requests to extend the access by driving the HTA pin high (that

is, deasserted).

Note:

HTA is driven in the Universal Bus modes (DCTR[HM]

=

$2 or

$3) while an external host is accessing the HI32. If the HI32 is

not accessed, the HTA pin is high impedance. The value of

HTAP can change only when DSR[HACT] = 0. HTAP is

ignored when the HI32 is not in a Universal Bus mode

(DCTR[HM]

≠

$2 or $3).

14

HRWP

0

UB

Host Read/Write Polarity

Controls the polarity of HWR/HRW signal in single-strobe Universal Bus

modes (DCTR[HM]

=

$2 or $3 and HDSM = 1); that is, when the

HWR/HRW signal (HP29) functions as the host read/write (HRW)

signal. When HRWP is cleared, the host-to-DSP data transfer direction

corresponds to the low level of the HRW signal, and DSP-to-host data

transfer direction corresponds to high level of the HRW signal. When

HRWP is set, the host-to-DSP data transfer direction corresponds to

the high level of the HRW signal, and DSP-to-host data transfer

direction corresponds to the low level of the HRW signal. The value of

HRWP can change only when DSR[HACT] = 0. HRWP is ignored when

the HI32 is not in a Universal Bus mode or double-strobe host port

mode is selected (DCTR[HM]

≠

$2 or $3, or HDSM = 0).

13

HDSM

0

UB

Host Data Strobe Mode

Controls the data strobe mode of the host port pins in a Universal Bus

mode (DCTR[HM] = $2 or $3). When HDSM is cleared, the

double-strobe pin mode is selected: the HWR/HRW pin (HP29)

functions as host write strobe HWR, and HRD/HDS (HP30) functions as

a host read strobe HRD. When HDSM is set, the single-strobe pin mode

is selected: the HWR/HRW pin functions as host read/write HRW and

HRD/HDS functions as host data strobe HDS. The value of HDSM can

change only when DSR[HACT] = 0 in the DSR. HDSM is ignored when

the HI32 is not in a Universal Bus mode (DCTR[HM]

≠

$2 or $3).

12–7

0

Reserved. Write to 0 for future compatibility.

6

HINT

0

UB/PCI

Host Interrupt A

Controls the HINTA pin. When the core sets HINT, the HINTA pin is

driven low. When the core clears HINT, the HINTA pin is released.

Table 6-10. DSP Control Register (DCTR) Bit Definitions (Continued)

Bit Number

Bit Name

Reset

Value

Mode

Description