3 essi status register (ssisr), Essi status register (ssisr) -28, Essi status register (ssisr) bit definitions -28 – Motorola DSP56301 User Manual

Page 226: 3 essi status register (ssisr), Figure 7-11. essi status register (ssisr)

ESSI Programming Model

7

-28

DSP56301 User’s Manual

7.5.3

ESSI Status Register (SSISR)

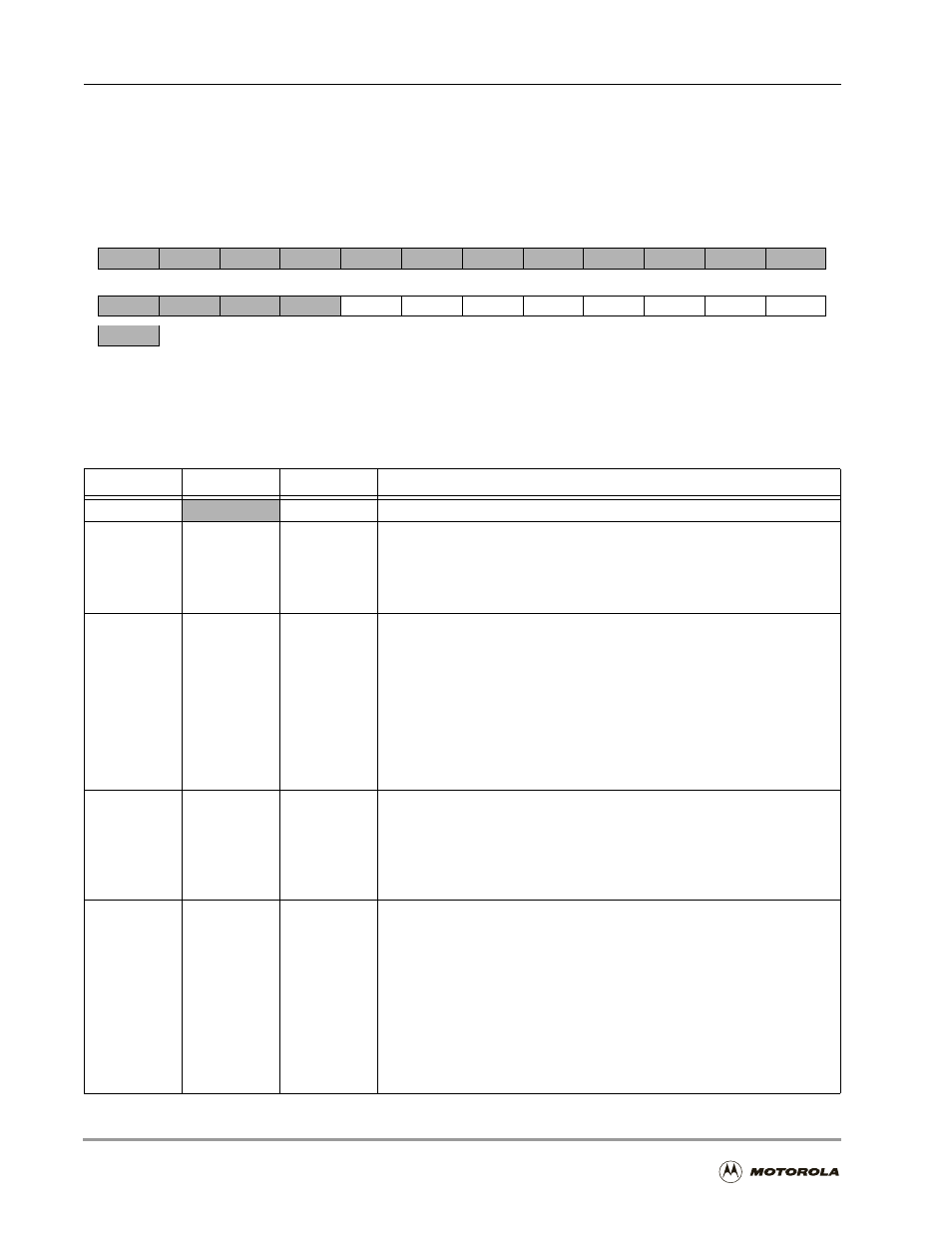

The SSISR is a read-only status register by which the DSP reads the ESSI status and serial

input flags.

Figure 7-11. ESSI Status Register (SSISR)

23

22

21

20

19

18

17

16

15

14

13

12

11

10

9

8

7

6

5

4

3

2

1

0

RDF

TDE

ROE

TUE

RFS

TFS

IF1

IF0

—Reserved bit; read as 0; write to 0 0 for future compatibility.

(ESSI0 X:$FFFFB7, ESSI1 X:$FFFFA7)

Table 7-5. ESSI Status Register (SSISR) Bit Definitions

Bit Number

Bit Name

Reset Value

Description

23–8

0

Reserved. Write to 0 for future compatibility.

7

RDF

0

Receive Data Register Full

Set when the contents of the receive shift register transfer to the receive

data register. RDF is cleared when the DSP reads the receive data

register. If RIE is set, a DSP receive data interrupt request is issued when

RDF is set.

6

TDE

0

Transmit Data Register Empty

Set when the contents of the transmit data register of every enabled

transmitter are transferred to the transmit shift register. It is also set for a

TSR disabled time slot period in Network mode (as if data were being

transmitted after the TSR has been written). When TDE is set, TDE data is

written to all the TX registers of the enabled transmitters or to the TSR.

The TDE bit is cleared when the DSP writes to all the transmit data

registers of the enabled transmitters, or when the DSP writes to the TSR

to disable transmission of the next time slot. If the TIE bit is set, a DSP

transmit data interrupt request is issued when TDE is set.

5

ROE

0

Receiver Overrun Error Flag

Set when the serial receive shift register is filled and ready to transfer to

the receive data register (RX) but RX is already full (that is, the RDF bit is

set). If the REIE bit is set, a DSP receiver overrun error interrupt request is

issued when the ROE bit is set. The programmer clears ROE by reading

the SSISR with the ROE bit set and then reading the RX.

4

TUE

0

Transmitter Underrun Error Flag

Set when at least one of the enabled serial transmit shift registers is empty

(that is, there is no new data to be transmitted) and a transmit time slot

occurs. When a transmit underrun error occurs, the previous data (which

is still present in the TX registers not written) is retransmitted. In Normal

mode, there is only one transmit time slot per frame. In Network mode,

there can be up to 32 transmit time slots per frame. If the TEIE bit is set, a

DSP transmit underrun error interrupt request is issued when the TUE bit

is set. The programmer can also clear TUE by first reading the SSISR with

the TUE bit set, then writing to all the enabled transmit data registers or to

the TSR.