2 host interface status register (hstr), Host interface status register (hstr) -56, 2 host interface status register (hstr) – Motorola DSP56301 User Manual

Page 174

Host-Side Programming Model

6

-56

DSP56301 User’s Manual

6.8.2

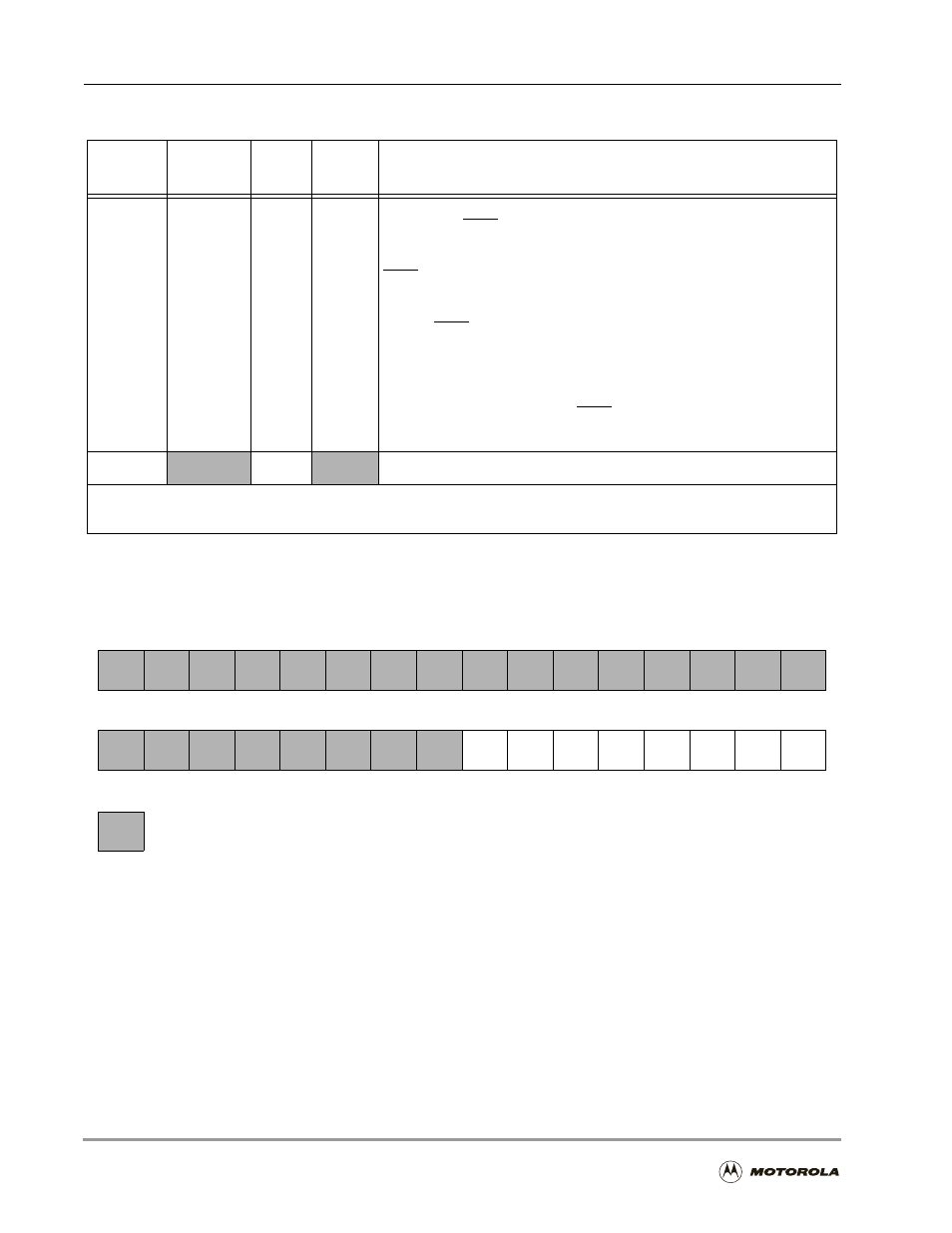

Host Interface Status Register (HSTR)

The HSTR is a 32-bit read-only status register by which the host processor examines the

status and flags of the HI32.

n

When the HSTR is read to the PCI bus (DCTR[HM]

=

$1), the

HAD[31– 0]

pins are

driven with the HSTR data during a read access.

n

In a 24-bit data Universal Bus mode (DCTR[HM]

=

$2 or $3 and HCTR[HRF] = $0),

the HD[23–0] pins are driven with the three least significant HSTR bytes during a read

access.

1

TREQ

0

UBM

Transmit Request Enable

Controls the HIRQ and HDRQ pins for host transmit data transfers in a

Universal Bus mode (DCTR[HM] = $2 or $3). When the DMA enable bit

(DMAE) is cleared, TREQ (when set) enables the Host Interrupt Request

HIRQ pin if the host transmit data request (HTRQ) status bit in the HI32

Status Register (HSTR) is set. If TREQ is cleared, HTRQ host interrupt

requests are disabled. If TREQ is set and HTRQ is set, the host interrupt

request HIRQ pin is asserted. HDRQ is deasserted.

When DMAE and the HSTR[HTRQ] status bit are set, TREQ enables the

host DMA request (HDRQ) pin. When TREQ is cleared, HTRQ external

DMA requests are disabled. If TREQ and HTRQ are set, the host DMA

request HDRQ pin is asserted. HIRQ is deasserted (high impedance if

HIRD = 0 in the DCTR). The personal hardware reset clears TREQ.

0

0

Reserved. Write to zero for future compatibility.

Note:

1.

High impedance if HIRD = 0 in the DCTR.

2.

High impedance if HIRD = 0 in the DCTR.

31

30

29

28

27

26

25

24

23

22

21

20

19

18

17

16

15

14

13

12

11

10

9

8

7

6

5

4

3

2

1

0

HREQ HINT

HF5

HF4

HF3 HRRQ HTRQ TRDY

UBM

PCI

UBM

PCI

UBM

PCI

UBM

PCI

UBM

PCI

UBM

PCI

UBM

PCI

UBM

PCI

Reserved, read as zero and should be written zero

UBM = Universal Bus mode

PCI = PCI mode

Figure 6-14. Host Interface Status Register (HSTR)

Table 6-22. Host Interface Control Register (HCTR) Bit Definitions (Continued)

Bit

Number

Bit Name

Reset

Value

Mode

Description