4 timer event counter (mode 3), Timer event counter (mode 3) -12, Event counter mode, trm = 1 -12 – Motorola DSP56301 User Manual

Page 274

Operating Modes

9

-12

DSP56301 User’s Manual

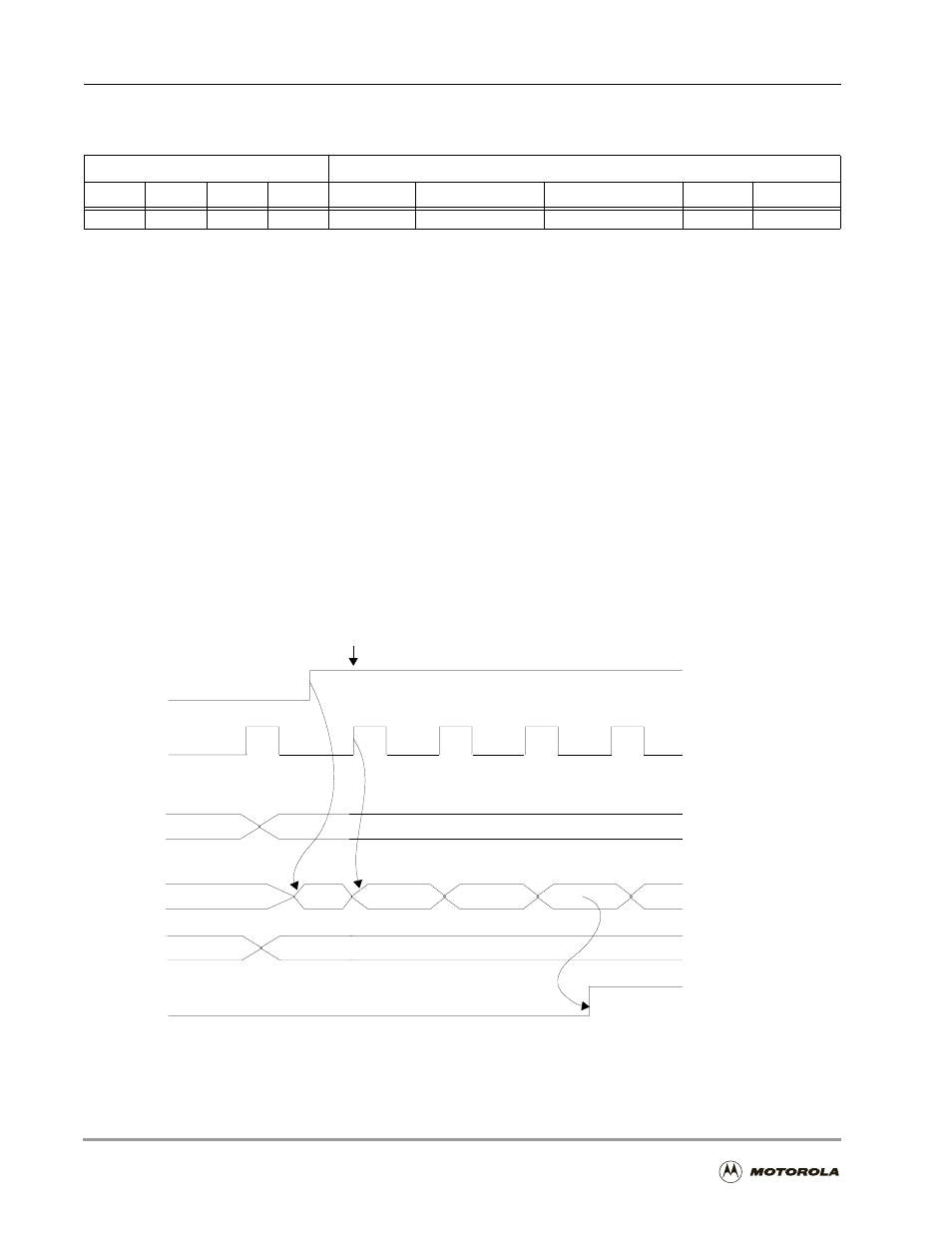

9.3.1.4 Timer Event Counter (Mode 3)

In Mode 3, the timer counts external events and issues an interrupt (if interrupt enable bits are

set) when the timer counts a preset number of events. The timer clock signal can be taken

from either the TIO input signal or the prescaler clock output. If an external clock is used, it

must be internally synchronized to the internal clock, and its frequency must be less than the

DSP56301 internal operating frequency divided by 4. The value of the TCSR[INV] bit

determines whether low-to-high (0 to 1) transitions or high-to-low (1 to 0) transitions

increment the counter. If the INV bit is set, high-to-low transitions increment the counter. If

the INV bit is cleared, low-to-high transitions increment the counter.

When the counter matches the value contained in the TCPR, TCSR[TCF] is set and a compare

interrupt is generated if the TCSR[TCIE] bit is set. If the TCSR[TRM] bit is set, the counter is

loaded with the value of the TLR when the next timer clock is received, and the count is

resumed. If the TCSR[TRM] bit is cleared, the counter continues to increment on each timer

clock. This process repeats until the timer is disabled.

Bit Settings

Mode Characteristics

TC3

TC2

TC1

TC0

Mode

Name

Function

TIO

Clock

0

0

1

1

3

Event Counter

Timer

Input

External

Figure 9-9. Event Counter Mode, TRM = 1

Mode 3 (internal clock): TRM = 1

N = write preload

M = write compare

TE

Clock

(TIO pin or prescale CLK)

TLR

TCPR

TCF (Compare Interrupt if TCIE = 1)

Counter (TCR)

first event

M

0

N

N + 1

M

N

N + 1

N

interrupts every

M - N clock

periods

if clock source

is from TIO pin,

TIO < CPUCLK + 4

NOTE: If INV = 1, counter is clocked on 1-to-0 clock transitions, instead of 0-to-1 transitions.