Motorola DSP56301 User Manual

Page 196

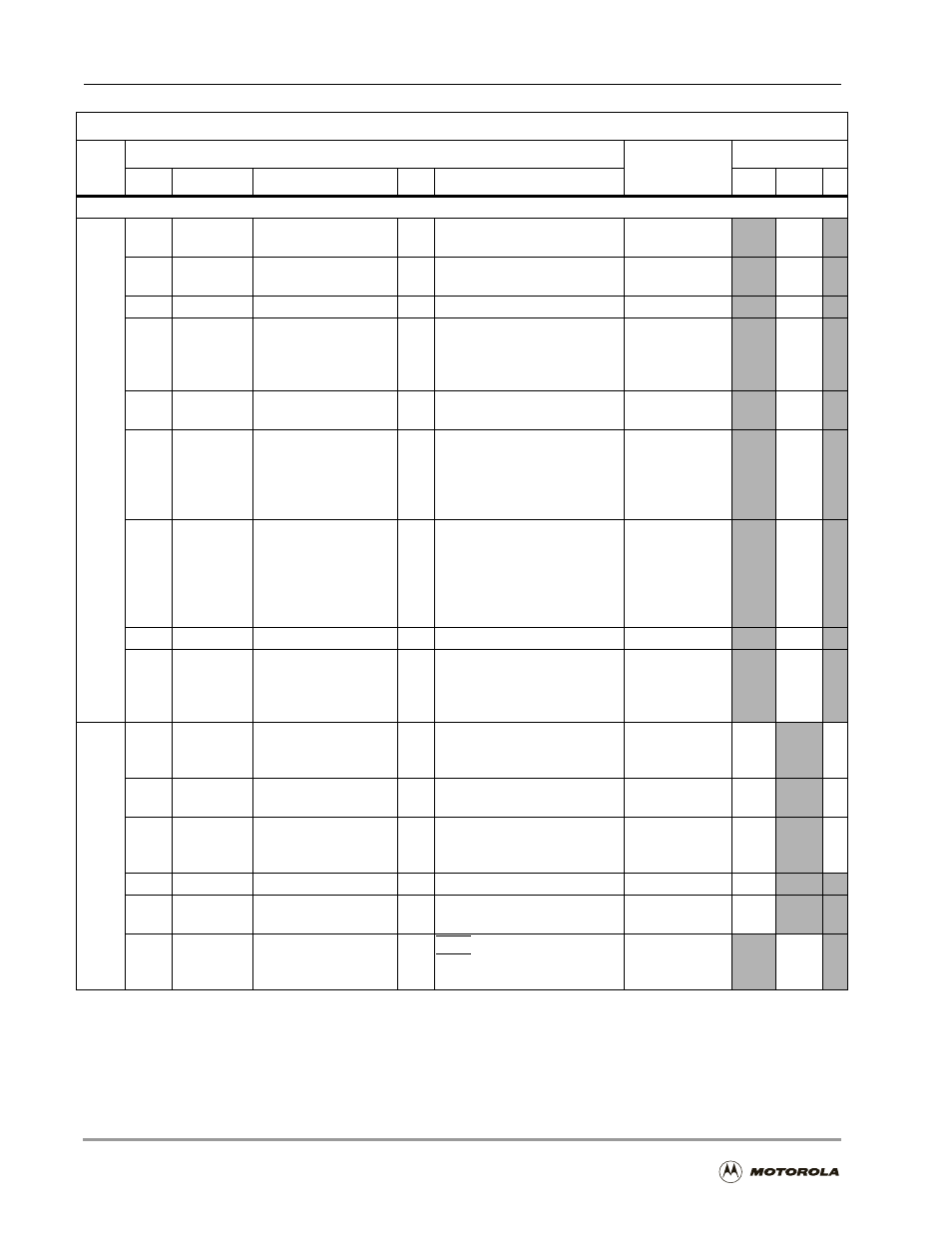

HI32 Programming Model/Quick Reference

6

-78

DSP56301 User’s Manual

Host Side

HCTR

1

TREQ

Transmit Request

Enable

0

1

HTRQ interrupt disabled

HTRQ interrupt enabled

-

0

-

2

RREQ

Receive Request

Enable

0

1

HRRQ interrupt disabled

HRRQ interrupt enabled

-

0

-

5-3

HF[2–0]

Host Flags

-

0

-

6

DMAE

DMA Enable

(ISA/EISA)

0

1

HI32 does not support DMA

transfers

HI32 supports ISA-DMA type

transfers

-

0

-

7

SFT

Slave Fetch Type

0

1

Pre-fetch

Fetch

-

0

-

9-8

HTF[1–0] Host Transmit Data

Transfer Format

00

01

10

11

PCI

UBM

32-bit mode

24-bit mode

3 LSBs

2 Right, zero ext.

3 LSBs

2 Right, sign ext.

3 MSbs

2 Left, zero filled

-

$0

-

12-11

HRF[1–0] Host Receive Data

Transfer Format

00

01

10

11

PCI

UBM

32-bit mode

24-bit mode

3 Right, zero ext.

2 LSBs

3 Right, sign ext.

2 LSBs

3 Left, zero filled

2 middle

bytes

-

$0

-

16-14

HS[2–0]

Host Semaphores

-

0

-

19

TWSD

Target Wait State

Disable

0

1

HI32 target inserts up to 8

wait states

HI32 target does not insert

wait states

-

0

-

HSTR

0

TRDY

Transmitter Ready

1

0

transmit FIF O (6 deep) is

empty

transmit FIFO is not empty

1

-

1

1

HTRQ

Host Transmit Data

Request

1

0

host transmit FIFO is not full

host transmit FIFO is full

1

-

1

2

HRRQ

Host Receive Data

Request

0

1

host receive FIFO is empty

host receive FIFO is not

empty

0

-

0

5-3

HF[5–3]

Host Flags

0

-

-

6

HINT

Host Interrupt A

0

1

HINTA pin is high impedance

HINTA pin is driven low

0

-

-

7

HREQ

Host Request

0

1

HIRQ pin is deasserted

HIRQ pin is asserted (if

enabled)

-

0

-

HI32 Registers—Quick Reference

Reg

Bit

Comments

Reset Type

Num

Mnemonic

Name

Val

Function

HS

PH

PS