6 on-chip memory, 5 internal buses, On-chip memory -10 – Motorola DSP56301 User Manual

Page 26: Internal buses -10, Dsp56301 switch memory configuration -10, 5 internal buses, Peripheral i/o expansion bus to peripherals

Internal Buses

1

-10

DSP56301 User’s Manual

1.4.6

On-Chip Memory

The memory space of the DSP56300 core is partitioned into program, X data, and Y data

memory space. The data memory space is divided into X and Y data memory in order to work

with the two address ALUs and to feed two operands simultaneously to the data ALU.

Memory space includes internal RAM and ROM and can be expanded off-chip under

software control. There is an on-chip 192/3K x 24-bit bootstrap ROM. For details on internal

memory, see Chapter 3,

Memory Configuration. Program RAM, instruction cache, X data

RAM, and Y data RAM size are programmable, as Table 1-2 shows.

1.5

Internal Buses

All internal buses on the DSP56300 devices are 24-bit buses. To provide data exchange

between the blocks, the DSP56301 implements the following buses:

n

Peripheral I/O expansion bus to peripherals

n

X memory expansion bus to X memory

n

Y memory expansion bus to Y memory

n

Program data bus for carrying program data throughout the core

n

X memory data bus for carrying X data throughout the core

n

Y memory data bus for carrying Y data throughout the core

n

Program address bus for carrying program memory addresses throughout the core

n

X memory address bus for carrying X memory addresses throughout the core

n

Y memory address bus for carrying Y memory addresses throughout the core.

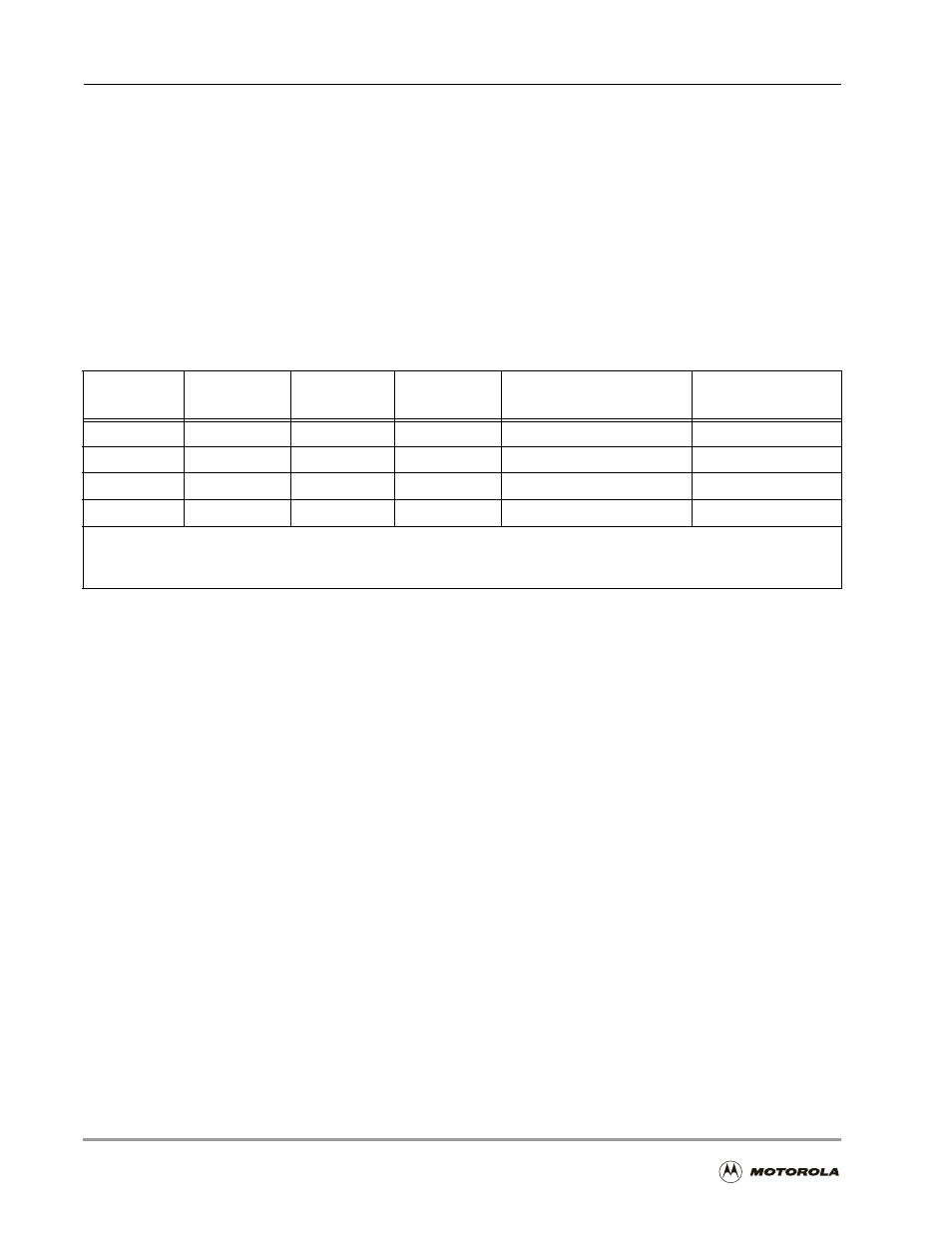

Table 1-2. DSP56301 Switch Memory Configuration

Program

RAM Size

Instruction

Cache Size

X Data RAM

Size

Y Data RAM

Size

Instruction Cache

1

Switch Mode

2

4096

×

24-bit

0

2048

×

24-bit

2048

×

24-bit

disabled (CE = 0)

disabled (MS = 0)

3072

×

24-bit

1024

×

24-bit

2048

×

24-bit

2048

×

24-bit

enabled (CE = 1)

disabled (MS = 0)

2048

×

24-bit

0

3072

×

24-bit

3072

×

24-bit

disabled (CE = 0)

enabled (MS = 1)

1024

×

24-bit

1024

×

24-bit

3072

×

24-bit

3072

×

24-bit

enabled (CE = 1)

enabled (MS = 1)

1.

Controlled by the Cache Enable (CE) bit in the Status Register (SR)

2.

Controlled by the Memory Select (MS) bit in the Operating Mode Register (OMR)